# **Granite River Labs**

GRL-PCIE5-CEM-RXA PCI Express Card Electromechanical (CEM) 5.0 (32 GT/s)

Receiver Compliance Test Automation Solution User Guide and MOI

Using GRL-PCIE5-CEM-RXA Automation Test Software,

Anritsu MP1900A BERT,

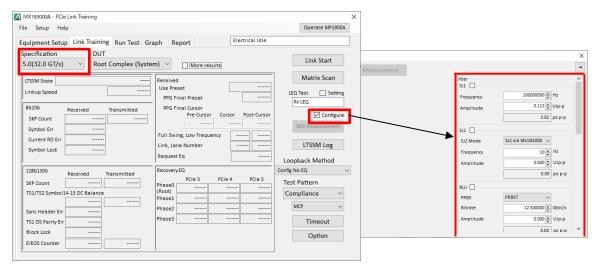

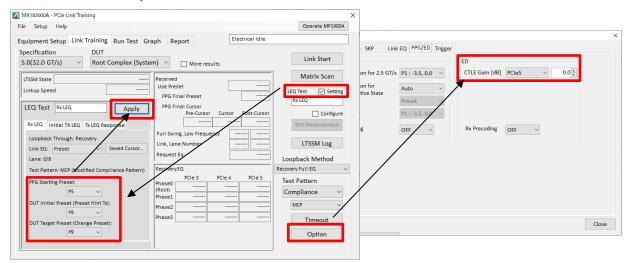

and

High Performance Oscilloscope

Published on 25 August 2022

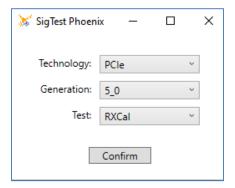

#### **DISCLAIMER**

This document is provided "as is" with no warranties whatsoever, including any warranty of merchantability, no infringement, fitness for any particular purpose, or any warranty otherwise arising out of any proposal, specification, or sample. The GRL disclaims all liability for infringement of proprietary rights, relating to use of information in this specification. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted herein.

All product names are trademarks, registered trademarks, or service marks of their respective owners.

Copyright © 2022 Granite River Labs. All rights reserved.

### **TABLE OF CONTENTS**

| 1 | IN                | TRO | DDUCTION                                                                                                                                 | 11 |

|---|-------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2 | RE                | SO  | URCE REQUIREMENTS                                                                                                                        | 12 |

|   | 2.1               | Eq  | UIPMENT REQUIREMENTS                                                                                                                     | 12 |

|   | 2.2               | So  | FTWARE REQUIREMENTS                                                                                                                      | 14 |

| 3 | SE                | TT  | ING UP GRL-PCIE5-CEM-RXA AUTOMATION SOFTWARE                                                                                             | 15 |

|   | 3.1               | Do  | WNLOAD GRL-PCIE5-CEM-RXA SOFTWARE                                                                                                        | 15 |

|   | 3.2               | Lau | JNCH AND SET UP SOFTWARE                                                                                                                 | 15 |

|   | 3.3<br>3.3        |     | e-Configure Software Before Calibration/Testing<br>Enter Test Session Information                                                        |    |

| 4 | CA                | LIE | BRATING USING GRL-PCIE5-CEM-RXA SOFTWARE                                                                                                 | 19 |

|   | 4.1<br>4.1        |     | r Up Automated Rx Calibration for TP3<br>TP3 Calibration Setup with Tektronix ATI Based Oscilloscope                                     |    |

|   | 4.2<br>4.2<br>4.2 | 2.1 | r Up Autoмated Rx Calibration for TP2<br>Connect Equipment for System Board Calibration<br>Connect Equipment for Add-In Card Calibration | 22 |

|   | 4.3               | SE  | r Measurement Conditions                                                                                                                 | 25 |

|   | 4.4<br>4.4        |     | r Up Calibration Requirements                                                                                                            |    |

|   | 4.5<br>4.5<br>4.5 | 5.1 | ECT PCIE CEM 5.0 Rx CALIBRATIONSelect to Perform TP3 CalibrationSelect to Perform Long Channel TP2 Calibration                           | 27 |

|   | 4.6               | Co  | NFIGURE CALIBRATION PARAMETERS                                                                                                           | 28 |

|   | 4.7               | Co  | NFIGURE CALIBRATION TARGET VALUES                                                                                                        | 32 |

|   | 4.8               | Rυ  | N AUTOMATION CALIBRATION                                                                                                                 | 32 |

| 5 | TE                | ST  | ING USING GRL-PCIE5-CEM-RXA SOFTWARE                                                                                                     | 34 |

|   | 5.1<br>5.1        |     | ERVIEW OF DUT Tx Preset Test                                                                                                             |    |

|   | 5.2<br>5.2        |     | ERVIEW OF DUT INITIAL TX EQUALIZATION TESTAdd-In Card Initial Tx Equalization Test at 32.0 GT/s                                          |    |

|   | 5.3<br>5.3        |     | ERVIEW OF DUT Tx LINK EQUALIZATION RESPONSE TESTSystem Board Tx Link Equalization Response Test at 32.0 GT/s                             |    |

|         | 5.3.2                                                                  | Add-In Card Tx Link Equalization Response Test at 32.0 GT/s                                                                                                   | 36             |

|---------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|         | 5.4 OVE<br>5.4.1<br>5.4.2<br>5.4.3                                     | RVIEW OF DUT RX LINK EQUALIZATION TESTSystem Board Rx Link Equalization Test at 32.0 GT/sAdd-In Card Rx Link Equalization Test at 32.0 GT/sLink Training      | 37<br>38       |

|         | 5.5 SET<br>5.5.1<br>5.5.2                                              | UP AUTOMATED DUT TXRX LINK EQUALIZATION TEST  Connect Equipment for System Board TxRx Link EQ Testing  Connect Equipment for Add-In Card TxRx Link EQ Testing | 40             |

|         | 5.6 SET<br>5.6.1<br>5.6.2                                              | UP AUTOMATED DUT Rx COMPLIANCE TEST                                                                                                                           | 42             |

|         | 5.7 Sет<br>5.7.1                                                       | UP TEST REQUIREMENTS                                                                                                                                          |                |

|         | 5.8 SEL<br>5.8.1<br>5.8.2                                              | ECT PCIE CEM 5.0 Rx TESTS<br>Select to Run DUT Link Training and Rx Compliance Test<br>Select to Run SJ Margin Search Test                                    | 46             |

|         | 5.9 Con                                                                | NFIGURE TEST PARAMETERS                                                                                                                                       | 47             |

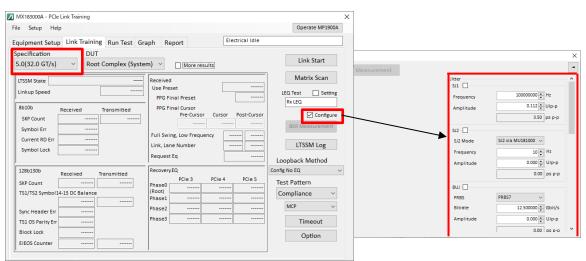

|         | 5.10 E                                                                 | NABLE LOOPBACK BER TEST                                                                                                                                       | 50             |

|         | 5.11 R                                                                 | UN AUTOMATION TESTS                                                                                                                                           | 51             |

| 6       | INTER                                                                  | PRETING GRL-PCIE5-CEM-RXA TEST REPORT                                                                                                                         | 53             |

|         | 6.1.1<br>6.1.2<br>6.1.3                                                | Test Session Information  Test Summary Table  Test Results                                                                                                    | 53<br>54<br>54 |

|         |                                                                        | ETE TEST RESULTS                                                                                                                                              |                |

| 7       |                                                                        | G AND LOADING GRL-PCIE5-CEM-RXA TEST SESSIONS                                                                                                                 | 55             |

| 8<br>5. |                                                                        | NDIX A: METHOD OF IMPLEMENTATION (MOI) FOR MANUAL<br>IVER MEASUREMENTS                                                                                        | PCIE CEM.      |

|         | 8.1 PER<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>8.1.5<br>8.1.6<br>8.1.7 | Calibration Settings                                                                                                                                          |                |

| 8.1.8<br>8.1.9                                                                                                                                                   | SJ Calibration                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

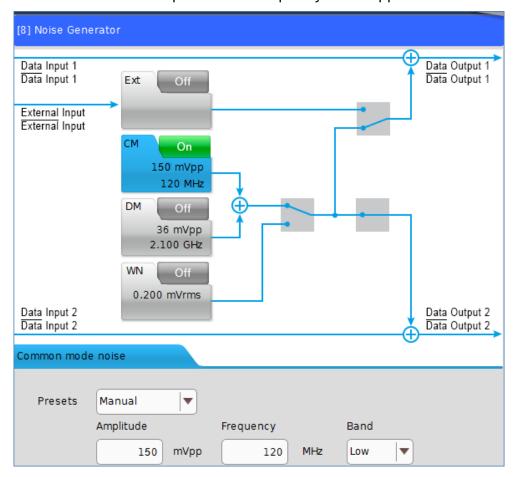

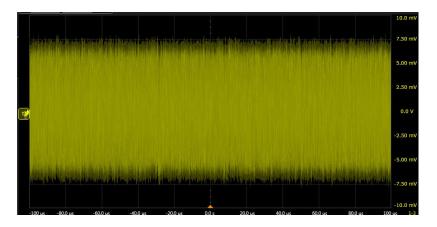

| 8.1.10                                                                                                                                                           | DM & CM Amplitude and Eye Height/Eye Width Calibration Setup                                                                                                                                                                                                                                                                                                                                                                                                                             | 74                                                      |

| 8.1.11<br>8.1.12                                                                                                                                                 | DM-I Calibration Adjustment<br>CM-I Calibration Adjustment                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                         |

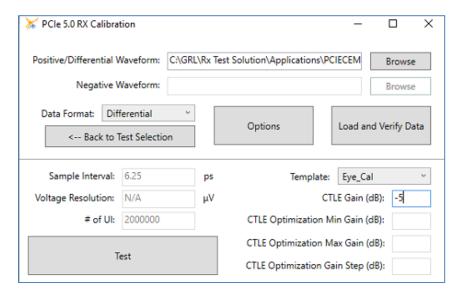

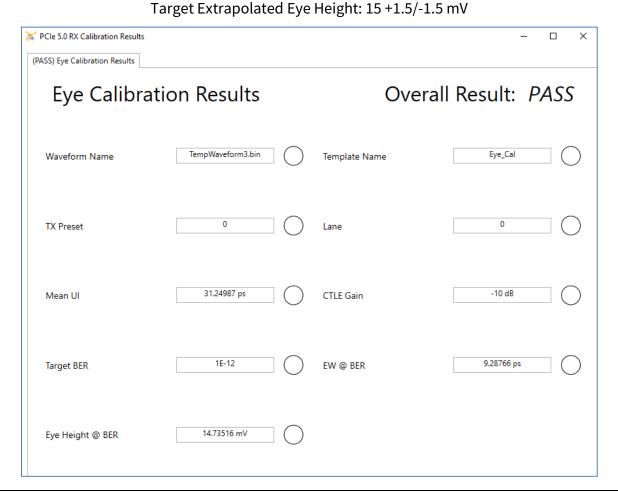

| 8.1.13                                                                                                                                                           | EH/EW Calibration Adjustment                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                         |

| 8.2 PEI<br>8.2.1                                                                                                                                                 | RFORM INITIAL TX EQUALIZATION & TX LINK EQUALIZATION RESPONSE TESTS<br>Equipment Setup for Add-in Card DUT Initial Tx EQ / Tx Link EQ Response                                                                                                                                                                                                                                                                                                                                           |                                                         |

| 8.2.2                                                                                                                                                            | Equipment Setup for System Board DUT Tx Link EQ Response Test                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                         |

| 8.2.3                                                                                                                                                            | Initial Tx EQ Startup and Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                         |

| 8.2.4                                                                                                                                                            | Tx Link EQ Time Response (with Presets/Cursors) Startup and Testing                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                         |

| 8.3 PEI<br>8.3.1                                                                                                                                                 | REPORM RX LINK EQ TEST                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                         |

| 8.3.1                                                                                                                                                            | Equipment Setup for Add-in Card DUT Loopback Test  Equipment Setup for System Board DUT Loopback Test                                                                                                                                                                                                                                                                                                                                                                                    |                                                         |

| 8.3.3                                                                                                                                                            | Link Training Initialization and Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                         |

| 8.3.4                                                                                                                                                            | Link Training Failure Troubleshooting                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 96                                                      |

|                                                                                                                                                                  | REFORM DUT RX COMPLIANCE TESTING                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                         |

| 8.4.1                                                                                                                                                            | Jitter Tolerance Testing (Optional)                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                         |

|                                                                                                                                                                  | NDIX B: RETURN PATH OPTIMIZATION USING ANRITSU J1890A                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                         |

|                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                         |

| DRIVER S                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 99                                                      |

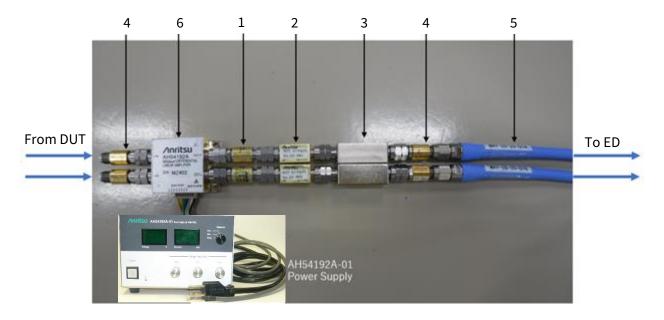

| 9.1 RE                                                                                                                                                           | QUIREMENTS FOR USING AN EXTERNAL DRIVER (J1890A)                                                                                                                                                                                                                                                                                                                                                                                                                                         | 99                                                      |

| 9.1 RE                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 99                                                      |

| 9.1 REG<br>9.2 REG<br>9.3 J18                                                                                                                                    | QUIREMENTS FOR USING AN EXTERNAL DRIVER (J1890A)                                                                                                                                                                                                                                                                                                                                                                                                                                         | 99<br>99<br>103                                         |

| 9.1 RE6<br>9.2 RE<br>9.3 J18<br>9.3.1                                                                                                                            | QUIREMENTS FOR USING AN EXTERNAL DRIVER (J1890A)  TURN PATH OPTIMIZATION PROCEDURE  B90A PCIE5 Re-Driver Set Setup & Configuration  Configuration of Re-Driver                                                                                                                                                                                                                                                                                                                           | 99<br>99<br>103<br>103                                  |

| 9.1 REG<br>9.2 REG<br>9.3 J18                                                                                                                                    | QUIREMENTS FOR USING AN EXTERNAL DRIVER (J1890A)                                                                                                                                                                                                                                                                                                                                                                                                                                         | 99<br>99<br>103<br>103                                  |

| 9.1 RE0<br>9.2 RE1<br>9.3 J18<br>9.3.1<br>9.3.2                                                                                                                  | QUIREMENTS FOR USING AN EXTERNAL DRIVER (J1890A)  TURN PATH OPTIMIZATION PROCEDURE  B90A PCIE5 Re-Driver Set Setup & Configuration  Configuration of Re-Driver                                                                                                                                                                                                                                                                                                                           | 99<br>99<br>103<br>103<br>104                           |

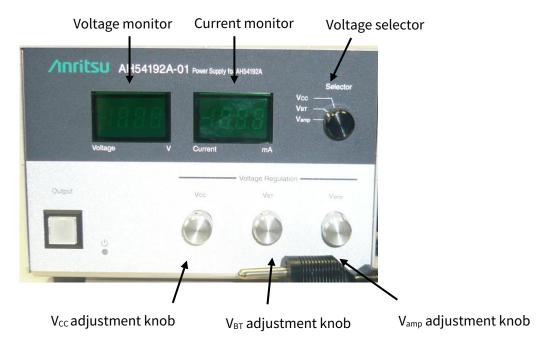

| 9.1 RE0<br>9.2 RE1<br>9.3 J18<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4                                                                                                | QUIREMENTS FOR USING AN EXTERNAL DRIVER (J1890A)  FURN PATH OPTIMIZATION PROCEDURE  B90A PCIE5 RE-DRIVER SET SETUP & CONFIGURATION.  Configuration of Re-Driver.  Connections.  Setting of Power Supply AH54192A-01.                                                                                                                                                                                                                                                                     | 99 99 103 103 104 105                                   |

| 9.1 REC<br>9.2 RET<br>9.3 J18<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4<br>10 APP                                                                                      | QUIREMENTS FOR USING AN EXTERNAL DRIVER (J1890A)  FURN PATH OPTIMIZATION PROCEDURE  B90A PCIE5 Re-Driver Set Setup & Configuration  Configuration of Re-Driver  Connections  Setting of Power Supply AH54192A-01  Voltage Setup Steps of AH54192A-01                                                                                                                                                                                                                                     | 99 99 103 103 104 105                                   |

| 9.1 REC<br>9.2 REC<br>9.3 J18<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4<br>10 APP<br>SOLUTIO                                                                           | QUIREMENTS FOR USING AN EXTERNAL DRIVER (J1890A)  FURN PATH OPTIMIZATION PROCEDURE  B90A PCIE5 RE-DRIVER SET SETUP & CONFIGURATION  Configuration of Re-Driver  Connections  Setting of Power Supply AH54192A-01  Voltage Setup Steps of AH54192A-01  FENDIX C: RETURN PATH OPTIMIZATION USING MACOM TECHNOLOGY.                                                                                                                                                                         | 99 99 103 103 104 105 DLOGY 106                         |

| 9.1 REC<br>9.2 REC<br>9.3 J18<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4<br><b>10 APP</b><br><b>SOLUTIO</b>                                                             | QUIREMENTS FOR USING AN EXTERNAL DRIVER (J1890A)  FURN PATH OPTIMIZATION PROCEDURE  B90A PCIE5 RE-DRIVER SET SETUP & CONFIGURATION  Configuration of Re-Driver  Connections  Setting of Power Supply AH54192A-01  Voltage Setup Steps of AH54192A-01  ENDIX C: RETURN PATH OPTIMIZATION USING MACOM TECHNOLOGY  ENS RE-DRIVER                                                                                                                                                            | 99 99 103 103 104 105 DLOGY 106 106                     |

| 9.1 REC<br>9.2 RET<br>9.3 J18<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4<br><b>10 APP</b><br><b>SOLUTIO</b><br>10.1 F<br>10.2 F<br>10.3 N                               | QUIREMENTS FOR USING AN EXTERNAL DRIVER (J1890A)  FURN PATH OPTIMIZATION PROCEDURE  B90A PCIe5 Re-Driver Set Setup & Configuration  Configuration of Re-Driver  Connections  Setting of Power Supply AH54192A-01  Voltage Setup Steps of AH54192A-01  ENDIX C: RETURN PATH OPTIMIZATION USING MACOM TECHNOLOGY  INS RE-DRIVER  REQUIREMENTS FOR USING AN EXTERNAL DRIVER (MACOM)  RETURN PATH OPTIMIZATION PROCEDURE  MACOM RE-DRIVER SETUP & CONFIGURATION                              | 99 99 103 103 104 105 DLOGY 106 106 106                 |

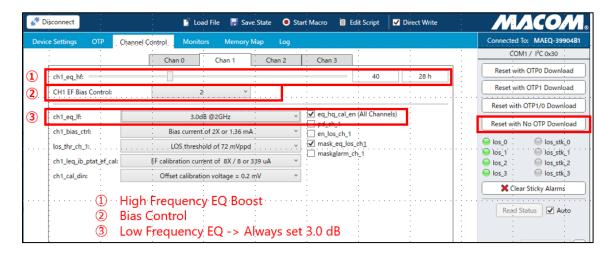

| 9.1 REC<br>9.2 REC<br>9.3 J18<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4<br><b>10 APP</b><br><b>SOLUTIO</b><br>10.1 F<br>10.2 F<br>10.3 N<br>10.3.1                     | QUIREMENTS FOR USING AN EXTERNAL DRIVER (J1890A)  FURN PATH OPTIMIZATION PROCEDURE  B90A PCIE5 RE-DRIVER SET SETUP & CONFIGURATION  Configuration of Re-Driver  Connections  Setting of Power Supply AH54192A-01  Voltage Setup Steps of AH54192A-01  EENDIX C: RETURN PATH OPTIMIZATION USING MACOM TECHNOLOGY  ENS RE-DRIVER  REQUIREMENTS FOR USING AN EXTERNAL DRIVER (MACOM)  RETURN PATH OPTIMIZATION PROCEDURE  MACOM RE-DRIVER SETUP & CONFIGURATION  Configuration of Re-Driver | 99 99 103 103 104 105 DLOGY 106 106 106 111             |

| 9.1 REC<br>9.2 RET<br>9.3 J18<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4<br><b>10 APP</b><br><b>SOLUTIO</b><br>10.1 F<br>10.2 F<br>10.3 N<br>10.3.1<br>10.3.2           | QUIREMENTS FOR USING AN EXTERNAL DRIVER (J1890A)                                                                                                                                                                                                                                                                                                                                                                                                                                         | 99 99 103 103 104 105 DLOGY 106 106 106 111 111         |

| 9.1 REC<br>9.2 RET<br>9.3 J18<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4<br><b>10 APP</b><br><b>SOLUTIO</b><br>10.1 F<br>10.2 F<br>10.3 N<br>10.3.1<br>10.3.2<br>10.3.3 | QUIREMENTS FOR USING AN EXTERNAL DRIVER (J1890A)  FURN PATH OPTIMIZATION PROCEDURE  B90A PCIE5 RE-DRIVER SET SETUP & CONFIGURATION  Configuration of Re-Driver  Connections  Setting of Power Supply AH54192A-01  Voltage Setup Steps of AH54192A-01  EENDIX C: RETURN PATH OPTIMIZATION USING MACOM TECHNOLOGY  ENS RE-DRIVER  REQUIREMENTS FOR USING AN EXTERNAL DRIVER (MACOM)  RETURN PATH OPTIMIZATION PROCEDURE  MACOM RE-DRIVER SETUP & CONFIGURATION  Configuration of Re-Driver | 99 99 103 103 104 105 DLOGY 106 106 106 111 111 111 111 |

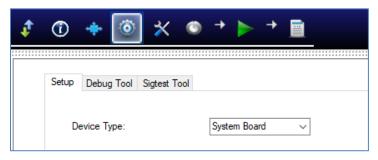

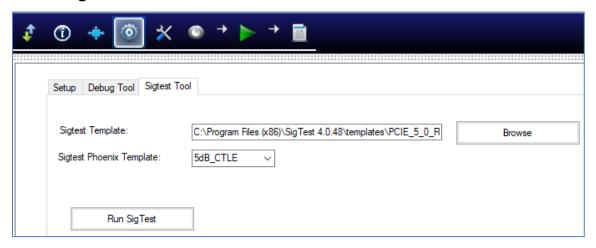

| 11 | APPENDIX D: SIGTEST TOOL TAB                        | 114 |

|----|-----------------------------------------------------|-----|

| 12 | APPENDIX E: DEBUG TOOL TAB                          | 116 |

| 13 | APPENDIX F: CONNECTING KEYSIGHT OSCILLOSCOPE TO PC  | 120 |

| 14 | APPENDIX G: CONNECTING TEKTRONIX OSCILLOSCOPE TO PC | 122 |

# **List of Figures**

| Figure 1. Select and Launch GRL Framework                                                                             | 5 |

|-----------------------------------------------------------------------------------------------------------------------|---|

| Figure 2. Start PCIe CEM 5.0 Rx Test Application                                                                      | 6 |

| Figure 3. See License Details10                                                                                       | 6 |

| Figure 4. Check License for Installed Applications10                                                                  | 6 |

| Figure 5. Connect Instruments with GRL Software18                                                                     | 8 |

| Figure 6. Session Info Page18                                                                                         | 8 |

| Figure 7. Rx Calibration Diagram from PHY Test Specification19                                                        | 9 |

| Figure 8. Recommended Setup for TP3 Rx Calibration                                                                    | 0 |

| Figure 9. Recommended Setup for TP3 Rx Calibration Using Tektronix ATI Scope2                                         | 1 |

| Figure 10. Recommended Setup for TP2 Long Channel Rx Calibration (PCIe Gen 5 System Board) 22                         | 2 |

| Figure 11. Recommended Setup for TP2 Long Channel Rx Calibration (PCIe Gen 5 System Board) Using Tektronix ATI Scope2 | 3 |

| Figure 12. Recommended Setup for TP2 Long Channel Rx Calibration (PCIe Gen 5 Add-In Card)24                           | 4 |

| Figure 13. Recommended Setup for TP2 Long Channel Rx Calibration (PCIe Gen 5 Add-In Card)                             |   |

| Using Tektronix ATI Scope2                                                                                            |   |

| Figure 14. Select Test Condition20                                                                                    |   |

| Figure 15. Set Up Calibration Requirements20                                                                          |   |

| Figure 16. Select Device for Calibration                                                                              |   |

| Figure 17. Select Rx Calibration2                                                                                     |   |

| Figure 18. Select TP3 Calibration2                                                                                    | 7 |

| Figure 19. Select Long Channel TP2 Calibration (with SigTest)28                                                       |   |

| Figure 20. Select Long Channel TP2 Calibration (with Seasim)28                                                        | 8 |

| Figure 21. Calibration Parameters Configuration Page29                                                                | 9 |

| Figure 22. Calibration Target Overwrite Page                                                                          | 2 |

| Figure 23. Run Tests Page                                                                                             | 3 |

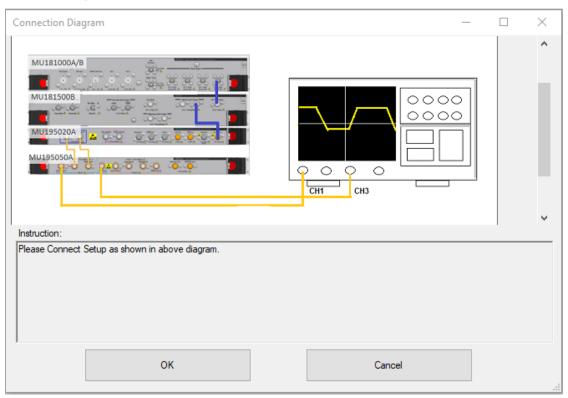

| Figure 24. Example Connection Pop-Up Diagram for Rx TP3 Calibration3                                                  | 3 |

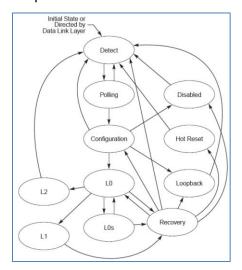

| Figure 25. Main State Diagram for Link Training and Status State Machine (from PHY Test Specification)39              | 9 |

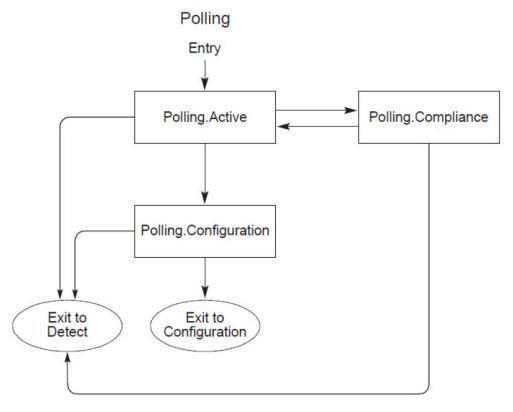

| Figure 26. Polling Substate Machine (from PHY Test Specification)                                                     |   |

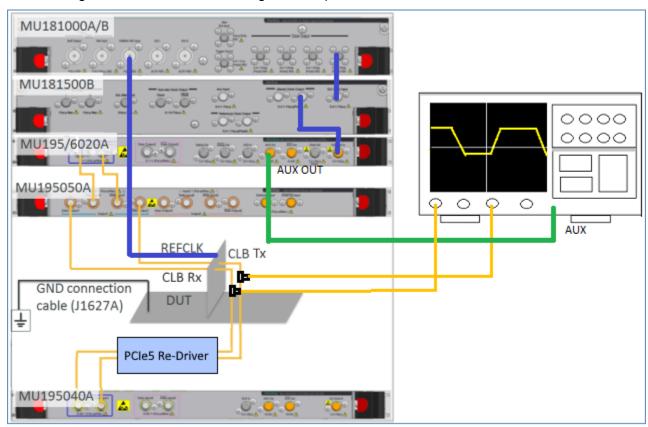

| Figure 27. Recommended Setup for DUT TxRx Link EQ Testing (PCIe Gen 5 System Board)                                   |   |

| Figure 28. Recommended Setup for DUT TxRx Link EQ Testing (PCIe Gen 5 Add-in Card)4                                   |   |

| Figure 29. Recommended Setup for DUT Rx Compliance Testing (PCIe Gen 5 System Board) 43                               |   |

| Figure 30. Recommended Setup for DUT Rx Compliance Testing (PCIe Gen 5 Add-In Card) 4-                                |   |

| Figure 31. Set Up Test Requirements4                                                                                  |   |

|                                                                                                                       |   |

| Figure 32. Select DUT Type                                                                             | 45   |

|--------------------------------------------------------------------------------------------------------|------|

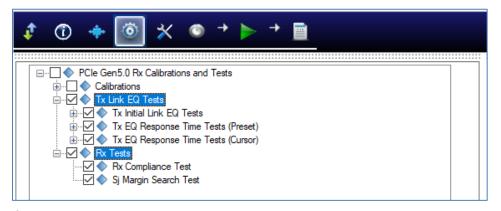

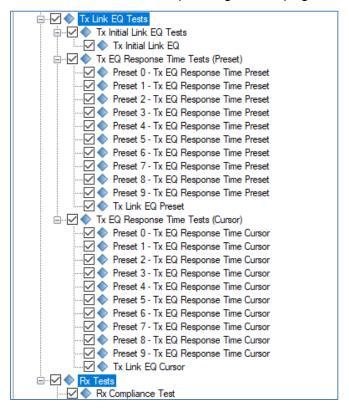

| Figure 33. Select Rx Tests                                                                             | 45   |

| Figure 34. Select DUT Tx Link EQ and Rx Compliance Tests                                               | 46   |

| Figure 35. Select SJ Margin Search Test                                                                | 46   |

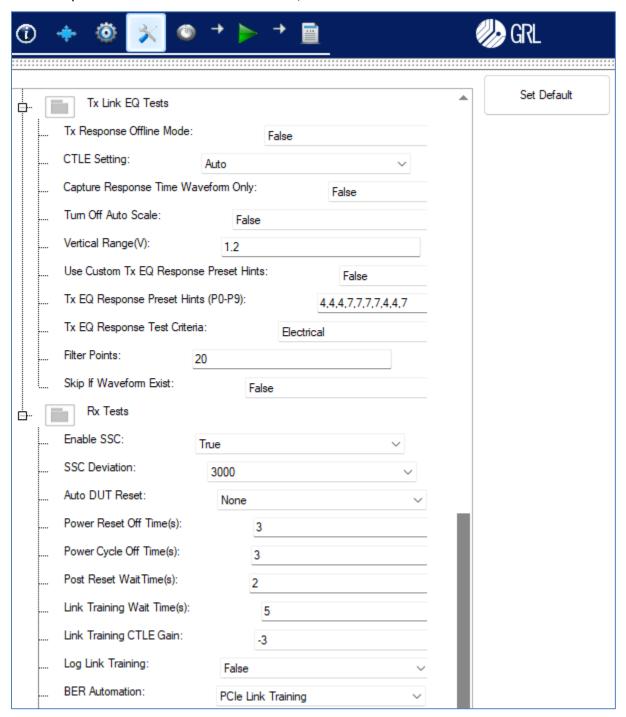

| Figure 36. Test Parameters Configuration Page                                                          | 47   |

| Figure 37. Connect Equipment for Loopback BER Test                                                     | 50   |

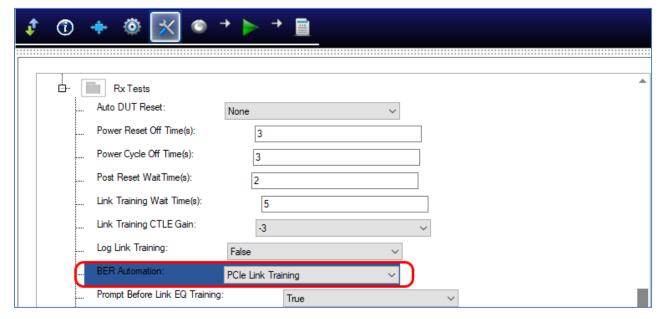

| Figure 38. Select BER Loopback Test Method                                                             | 50   |

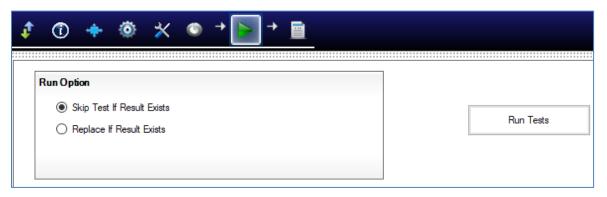

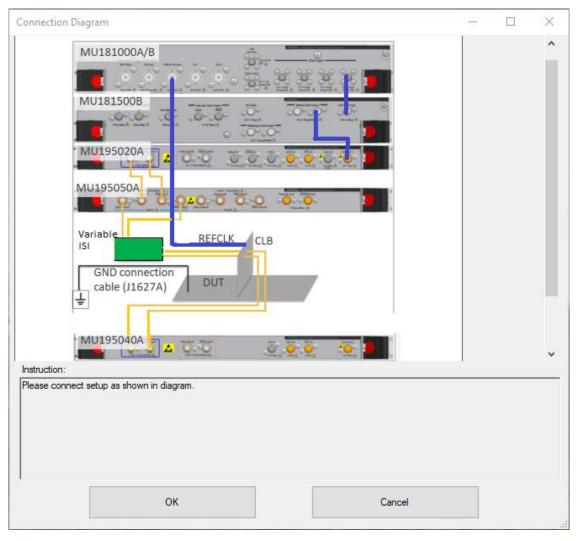

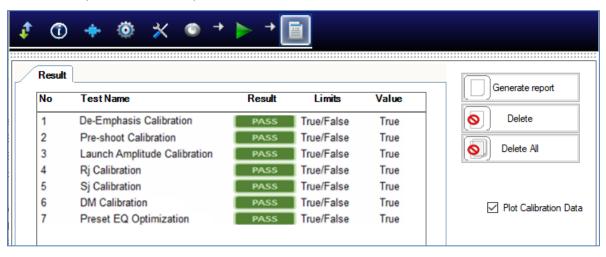

| Figure 39. Run Tests Page                                                                              | 51   |

| Figure 40. Example Connection Pop-Up Diagram for Rx Compliance Test                                    | 52   |

| Figure 41. Test Report Page                                                                            | 53   |

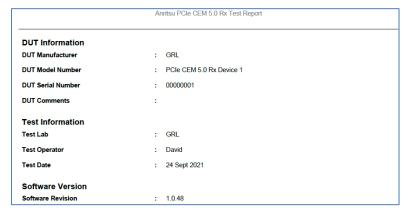

| Figure 42. Test Session Information Example                                                            | 53   |

| Figure 43. Test Summary Table Example                                                                  | 54   |

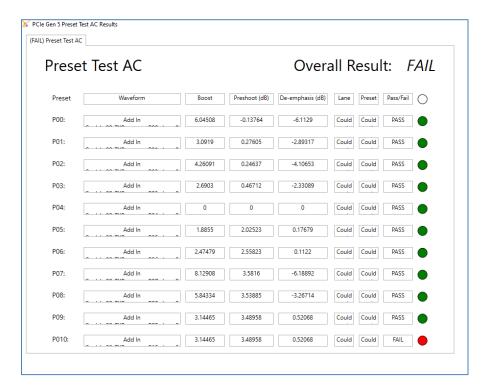

| Figure 44. Test Results Example                                                                        | 54   |

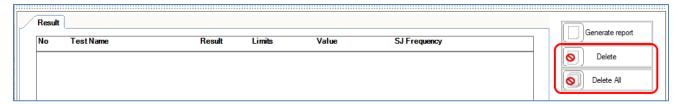

| Figure 45. Delete Test Results                                                                         | 55   |

| Figure 46. Save/Load/Create Test Sessions                                                              | 55   |

| Figure 47. PHY Test Specification Rx Calibration Diagram for PCIe Gen 5                                | 58   |

| Figure 48. Connection Diagram for Channel Loss Calibration (Add-In Card)                               | 59   |

| Figure 49. Connection Diagram for Channel Loss Calibration (System Board)                              | 59   |

| Figure 50. Connection Diagram for Amplitude, Preset, SJ and RJ Calibration                             | 60   |

| Figure 51. Connection Diagram for PCIe Gen 5 DM-I, CM-I and EH/EW TP2 Calibration (for Syste<br>Board) |      |

| Figure 52. Connection Diagram for PCIe Gen 5 DM-I, CM-I and EH/EW TP2 Calibration (for Add-I<br>Card)  |      |

| Figure 53. Connection Diagram for PCIe Gen 5 Add-in Card DUT Initial Tx EQ / Tx Link EQ Respo<br>Test  |      |

| Figure 54. Connection Diagram for PCIe Gen 5 System Board DUT Tx Link EQ Response Test                 | 83   |

| Figure 55. Connection Diagram for PCIe Gen 5 Add-in Card DUT Loopback Test                             | 92   |

| Figure 56. Connection Diagram for PCIe Gen 5 System Board DUT Loopback Test                            | 93   |

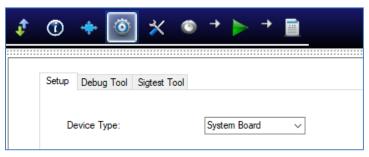

| Figure 57. Setup Configuration Page                                                                    | .114 |

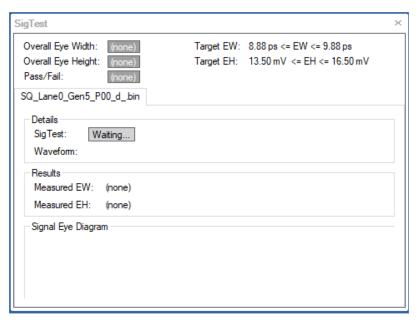

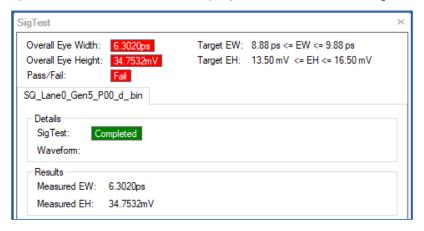

| Figure 58. Perform SigTest Debugging                                                                   | .114 |

| Figure 59. Running Offline SigTest Verification                                                        | .115 |

| Figure 60. Viewing SigTest Analysis Results                                                            | .115 |

| Figure 61. Setup Configuration Page                                                                    |      |

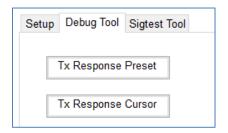

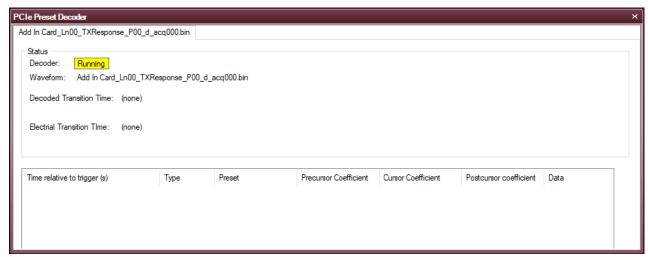

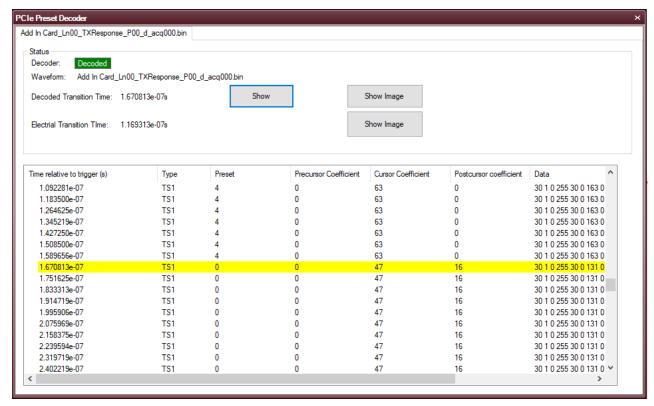

| Figure 62. Perform Tx Link EQ Time Response Offline Tests Debugging                                    |      |

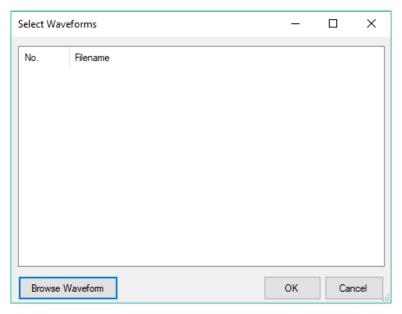

| Figure 63. Initiate Tx Link EQ Time Response Preset/Cursor Test                                        | .117 |

| Figure 64. Running Tx Link EQ Time Response Preset/Cursor Test                           | 117 |

|------------------------------------------------------------------------------------------|-----|

| Figure 65. Viewing Tx Link EQ Time Response Preset/Cursor Test Results                   | 118 |

| Figure 66. Viewing Tx Link EQ Time Response Preset/Cursor Test Trace for Transition Time | 119 |

| Figure 67. Keysight Connection Expert                                                    | 120 |

| Figure 68. Oscilloscope's VISA Address                                                   | 121 |

| Figure 69. OpenChoice Instrument Manager In Start Menu                                   | 122 |

| Figure 70. OpenChoice Instrument Manager Menu                                            | 123 |

# **List of Tables**

| Table 1. Equipment Requirements – Systems and Accessories | 12 |

|-----------------------------------------------------------|----|

| Table 2. Equipment Requirements – Cables                  | 13 |

| Table 3. Software Requirements                            | 14 |

| Table 4. Calibration Parameters Description               | 30 |

| Table 5. Test Parameters Description                      | 48 |

| Table 6. Calibration Settings                             |    |

| Table 7. Calibration Targets                              |    |

|                                                           |    |

# 1 Introduction

This user manual provides information using the GRL-PCIE5-CEM-RXA test automation solution to set up and test an electrical receiver (Rx) device to meet PCI Express Card Electromechanical (CEM) 5.0 compliance for 32 GT/s as per PCI Express (PCI-SIG) Standards.

The main body of this documentation first describes how to configure the GRL-PCIE5-CEM-RXA test software to calibrate the stressed eye at the receiver of the device under test (DUT) in the PCIe Gen 5.0 system. This includes calibration to be performed at both the physical Test Point 3 (TP3) and the Long Channel at TP2. The GRL software will automate calibration without channel effect at TP3 before measuring the eye opening due to trace length. It also enables running the SigTest and Seasim post processing analysis application to ensure signal quality compliance. The final calibrated eye diagram uses both the SigTest and Seasim software to achieve the final stressed eye calibration.

After completing calibration, the GRL-PCIE5-CEM-RXA software will automate compliance testing for the receiver using Bit Error Ratio (BER) as a metric. The receiver path is tested with worst case eye to ensure a BER of less than 1E-12 can be achieved. The software also provides an optional SJ margin search test for the DUT.

The GRL-PCIE5-CEM-RXA software performs test automation according to PCI-SIG-approved Methods of Implementation (MOI's) with high performance real-time oscilloscopes and Anritsu BERT using existing PCI-SIG Compliance Base Boards (CBB's) and Compliance Load Boards (CLB's). The GRL software is run from the computer or oscilloscope to provide automation control to test the DUT for PCIe CEM 5.0 Rx electrical compliance. When combined with a satisfactory level of interoperability testing, these tests provide a reasonable level of confidence that the DUT's will function properly in most PCIe environments.

Note: For manual test methodology, refer to Appendix of this documentation or PCI-SIG for approved Method of Implementation (MOI's) as technical reference.

# **2 Resource Requirements**

Note: Equipment requirements may vary according to the lab setup and DUT board. Below are the recommended lists of equipment for the typical test setup.

# 2.1 Equipment Requirements

TABLE 1. EQUIPMENT REQUIREMENTS – SYSTEMS AND ACCESSORIES

| System & Accessory                          | Qty. | Description/Key Spec Requirement                                                                                                  |

|---------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------|

| High Performance Real-time Oscilloscope [a] | 1    | ≥ 50 GHz bandwidth <sup>[b]</sup>                                                                                                 |

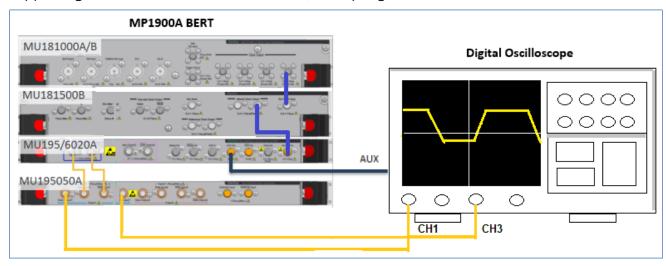

| Anritsu MP1900A BERT                        |      | MP1900A Signal Quality Analyzer, with following modules:                                                                          |

|                                             |      | MU181000A/B 12.5 GHz Synthesizer <sup>[c]</sup>                                                                                   |

|                                             |      | MU181500B Jitter Modulation Source                                                                                                |

|                                             |      | <ul> <li>MU195020A 21G/32G bit/s SI Pulse Pattern<br/>Generator, or</li> </ul>                                                    |

|                                             |      | MU196020A 64.2G bit/s or 64.2G baud<br>PAM4 Pulse Pattern Generator <sup>[d]</sup>                                                |

|                                             |      | MU195040A 21G/32G bit/s SI Error     Detector                                                                                     |

|                                             |      | MU195050A Noise Generator                                                                                                         |

| PCI-SIG Compliance Base Board (CBB)         | 1    | For add-in cards                                                                                                                  |

| PCI-SIG Compliance Load Board (CLB)         |      | For host system boards                                                                                                            |

| ISI Source Generator                        | 1    | Compliant Variable ISI channel                                                                                                    |

| Pick-off Tee                                | 2    | For connecting scope to CLB/CBB Tx lanes to perform link equalization tests                                                       |

| Terminator                                  | 1    | J1632A Coaxial Terminator, for termination of<br>unused MU195020A/MU196020A Aux Out<br>connector during link equalization testing |

| V(m) - K(f) Adapter                         | 2    | 34VKF50A Coaxial Adapter, only required if using a PAM4 Pulse Pattern Generator                                                   |

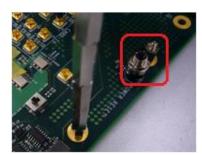

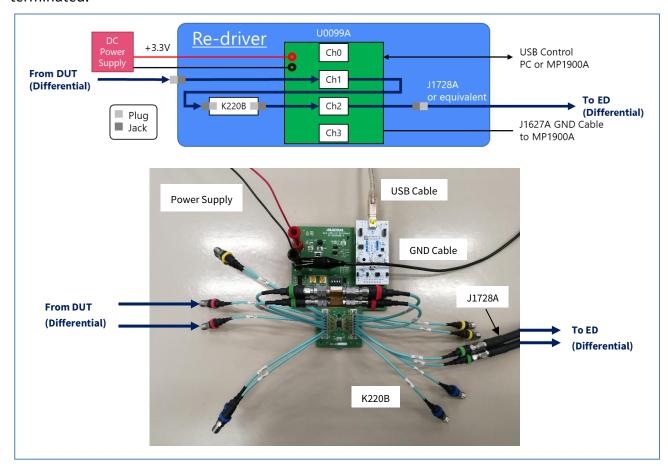

| PCIe5 Re-Driver                             |      | J1890A <sup>[e]</sup> PCIe5 Re-Driver Set with AH54192A <sup>[e]</sup><br>56Gbaud Differential Linear Amplifier                   |

|                                             |      | or                                                                                                                                |

|                                             |      | MACOM Technology Solutions Re-Driver [f]                                                                                          |

|                                             |      | For Return Path optimization in the System Tx/Rx<br>Link Equalization Test                                                        |

| System & Accessory           | Qty. | Description/Key Spec Requirement |

|------------------------------|------|----------------------------------|

| Computer (laptop or desktop) | 1    | Windows 7+ OS                    |

|                              |      | For automation control           |

<sup>&</sup>lt;sup>[a]</sup> Oscilloscope with scope software requirements as specified in vendor specific MOI's. For example, when using the Keysight Scope, scope software such as Keysight InfiniiSim / EZ-JIT / Serial Data Analysis / Serial Data Equalization that are required for testing and signal processing must be pre-installed on the Scope. Similarly, the Tektronix Scope shall be used with DPOJET (Jitter and Eye Analysis Tools) software for making measurements.

TABLE 2. EQUIPMENT REQUIREMENTS - CABLES

| Cable [a]                                                         | Qty.    |

|-------------------------------------------------------------------|---------|

| SMA-to-SMA cable                                                  | 4       |

| SMA coaxial cables                                                | 1 pair  |

| Phase matched K-K coaxial cables                                  | 3 pairs |

| J1746A K-K cable set (to connect between MU195020A and MU195050A) | 1       |

| J1627A GND connection cable                                       |         |

| BNC-to-SMA cable                                                  |         |

<sup>[</sup>a] Based on the standard test configuration. May require more or less cables depending on the DUT type.

<sup>[</sup>b] Oscilloscope with scope bandwidth as specified in vendor specific MOI's.

<sup>[</sup>c] MU181000B Option 02 is required for testing the System Board DUT.

<sup>[</sup>d] The GRL-PCIE5-CEM-RXA software supports PAM4 PPG in NRZ mode.

<sup>[</sup>e] The J1890A and AH54192A are packaged separately. Check the contents of both boxes. The AH54192A is supplied as a set with dedicated power supply AH54192A-01. See Appendix B for more details.

<sup>[</sup>f] See Appendix C for more details.

# 2.2 Software Requirements

TABLE 3. SOFTWARE REQUIREMENTS

| Software                                                           | Description/Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GRL-PCIE5-CEM-RXA                                                  | Granite River Labs PCI Express Card Electromechanical 5.0 (32 GT/s) Automated Receiver Calibration and Compliance Test Solution – www.graniteriverlabs.com                                                                                                                                                                                                                                                                                                                                                                                              |

| VISA (Virtual Instrument<br>Software Architecture)<br>API Software | VISA Software is required to be installed on the controller PC running GRL-PCIE5-CEM-RXA software. GRL's software framework has been tested to work with all three versions of VISA available on the Market:  1. NI-VISA: <a href="http://www.ni.com/download/ni-visa-17.0/6646/en/">http://www.ni.com/download/ni-visa-17.0/6646/en/</a> 2. Keysight IO Libraries: <a href="http://www.keysight.com">www.keysight.com</a> (Search on IO Libraries) 3. Tektronix TekVISA: <a href="http://www.tek.com">www.tek.com</a> (Downloads > Software > TekVisa) |

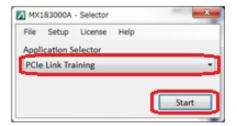

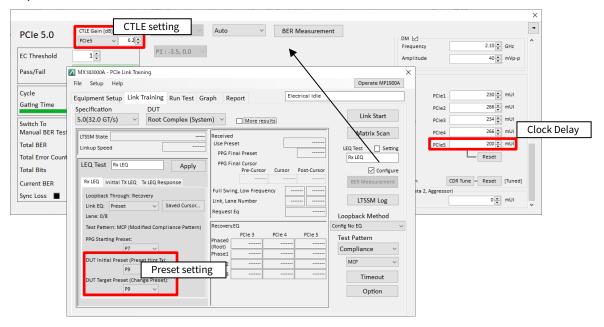

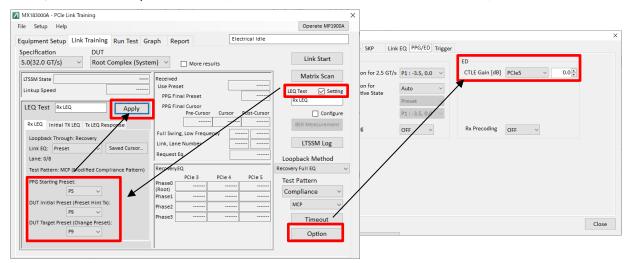

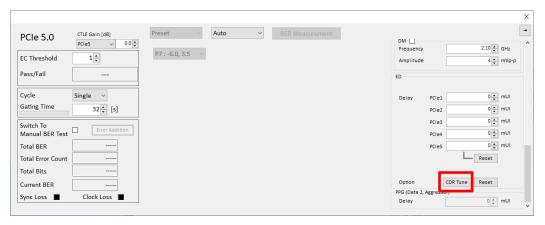

| MX183000A                                                          | Anritsu High-Speed Serial Data Test Software – For loopback BER testing of the PCIe Gen 5 CEM DUT receiver. This software is located in the MP1900A BERT.                                                                                                                                                                                                                                                                                                                                                                                               |

| SigTest Application                                                | Standard Post Processing Analysis Software – www.intel.com/content/www/us/en/design/technology/high-speed-io/tools.html                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Seasim                                                             | Seasim tool for post-process analysis of the captured waveform (Eye Opening simulation software) – <a href="https://www.pcisig.com">www.pcisig.com</a>                                                                                                                                                                                                                                                                                                                                                                                                  |

# 3 Setting Up GRL-PCIE5-CEM-RXA Automation Software

This section provides the procedures to start up and pre-configure the GRL-PCIE5-CEM-RXA automation software before running tests. It also helps users familiarize themselves with the basic operation of the software.

Note: The GRL software installer will automatically create shortcuts in the Desktop and Start Menu when installing the software.

To start using the GRL software, follow the procedures in the following sections.

#### **Download GRL-PCIE5-CEM-RXA Software** 3.1

Download and install the GRL software as follows:

- 1. If the GRL software is to be installed on a PC (where it is referred to as 'controller PC'), install VISA (Virtual Instrument Software Architecture) on to the PC where GRL-PCIE5-CEM-RXA is to be used (see Section 2.2).

- 2. Download the software ZIP file package from the Granite River Labs support site.

- 3. The ZIP file contains:

- PCIECEMGen5\_AN\_PatternFilesInstallationxxxxxxxxSetup.exe Run this on the Anritsu MP1900A BERT Signal Quality Analyzer to install the pattern setup files.

- PCIECEMGen5\_AN\_RxTestApplicationxxxxxxxxxSetup.exe Run this on the PC or on the oscilloscope to install the application.

- PCIECEMGen5\_AN\_RxTestScopeSetupFilesInstallationxxxxxxxxxSetup.exe Run this on the oscilloscope to install the scope setup files.

#### 3.2 **Launch and Set Up Software**

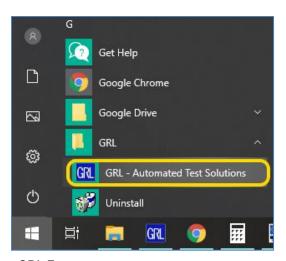

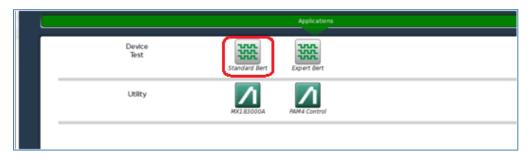

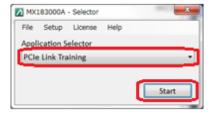

1. Once the software is installed, open the GRL folder from the Windows Start menu. Click on GRL - Automated Test Solutions within the GRL folder to launch the GRL software framework.

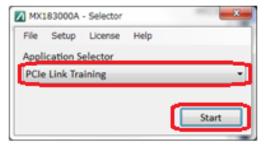

FIGURE 1. SELECT AND LAUNCH GRL FRAMEWORK

© Granite River Labs 2022

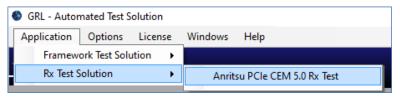

2. From the Application→Rx Test Solution drop-down menu, select 'Anritsu PCIe CEM 5.0 Rx Test' to start the PCIe CEM 5.0 Rx Test Application. If the selection is grayed out, it means that your license has expired.

FIGURE 2. START PCIE CEM 5.0 RX TEST APPLICATION

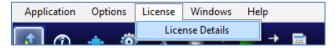

3. To enable license, go to License → License Details.

FIGURE 3. SEE LICENSE DETAILS

a) Check the license status for the installed application.

FIGURE 4. CHECK LICENSE FOR INSTALLED APPLICATIONS

- b) Activate a License:

- If you have an Activation Key, enter it in the field provided and select "Activate".

• If you do not have an Activation Key, select "Close" to use a demo version of the software over a free 10-day trial period.

**Note:** Once the 10-day trial period ends, you will need to request an Activation Key to continue using the software on the same computer or oscilloscope. The demo software is also limited in its capability, in that it will only calibrate the maximum frequency for each data rate. Thus, the demo version cannot be used to fully calibrate and test a device. For Demo and Beta Customer License Keys, please request an Activation Key by contacting <a href="mailto:support@graniteriverlabs.com">support@graniteriverlabs.com</a>.

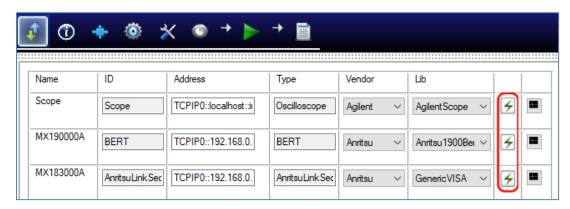

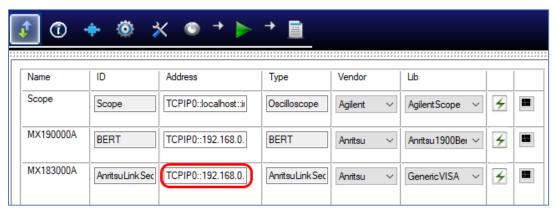

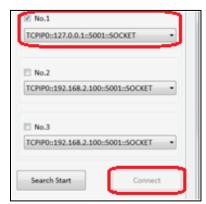

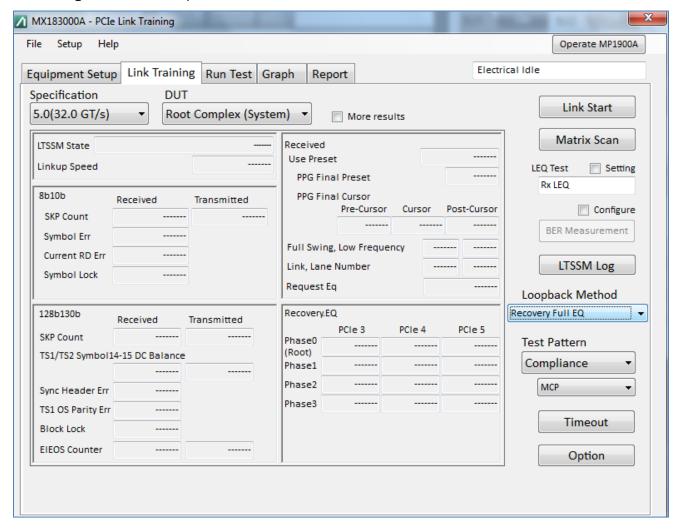

- 4. Select the Equipment Setup icon on the PCIe CEM 5.0 Rx Test Application menu.

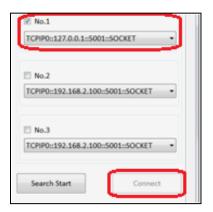

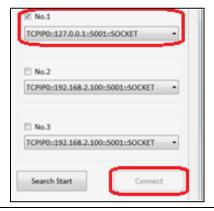

- 5. Connect the Anritsu MP1900A BERT via LAN to the GRL automation control enabled Scope or PC. The BERT and MX183000A software can be connected using connection string formats similar to the following examples:

- BERT: "TCPIP0::192.168.0.14::5001::SOCKET" or "192.168.0.14:5001"

- MX183000A: "TCPIP0::192.168.0.14::5000::SOCKET" or "192.168.0.14:5000"

Note the IP addresses listed above are only examples and should be changed according to the actual network connection being used.

- 6. On the Scope or controller PC, obtain the network addresses for all the connected instruments from the device settings. Note these addresses as they will be used to connect the instruments to the GRL automation software.

- 7. On the Equipment Setup page of the GRL PCIe CEM 5.0 Rx Test Application, type in the address of each connected instrument into the 'Address' field.

(Note: If the GRL software is installed on the **Tektronix Scope**, ensure the Scope is connected via GPIB and type in the GPIB network address, for example "GPIB8::1::INSTR".)

If the GRL software is installed on the PC to control the Scope, type in the Scope IP address, for example "TCPIP0::192.168.0.110::inst0::INSTR". Note to **omit** the Port number from the address.

(Note: If the GRL software is installed on the **Keysight Scope**, and if there is error in connection, type in the Scope IP address as "TCPIP0::192.168.0.4::5025::SOCKET".)

8. Then select the "lightning" button ( 1/2 ) for each connected instrument.

The "lightning" button should turn green ( ) once the software has successfully established connection with each instrument.

FIGURE 5. CONNECT INSTRUMENTS WITH GRL SOFTWARE

Note: Additional information for connecting supported vendor oscilloscopes (Keysight and Tektronix) to the PC is provided in the Appendix of this document.

## 3.3 Pre-Configure Software Before Calibration/Testing

Once all equipment is successfully connected from the previous section, proceed to set up the preliminary settings before going to the advanced measurement setup.

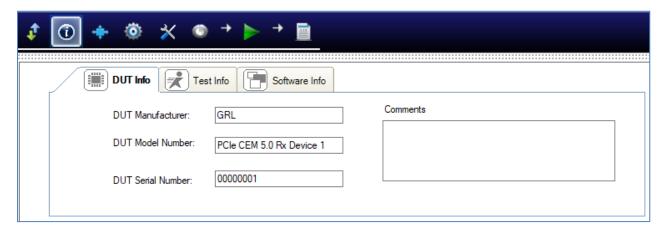

#### 3.3.1 Enter Test Session Information

Select from the menu to access the **Session Info** page. Enter the information as required for the test session that is currently being run. The information provided will be included in the test report generated by the software once tests are completed.

- The fields under **DUT Info** and **Test Info** are defined by the user.

- The Software Info field is automatically populated by the software.

FIGURE 6. SESSION INFO PAGE

# 4 Calibrating Using GRL-PCIE5-CEM-RXA Software

The GRL-PCIE5-CEM-RXA test solution supports automated Rx calibration using the SigTest and Seasim signal quality and stress tolerance analysis application for PCIe Gen 5 system boards and add-in cards. To perform calibration, the GRL-PCIE5-CEM-RXA software is run from the PC or oscilloscope to enable automation control for each step of calibration and signal quality test sequence.

Calibration for the PCIe CEM 5.0 electrical specification will basically be performed at two physical test points: TP3 and TP2 (for the Long Channel). Test Point 3 (TP3) is a physical test point for calibration without the effect of a channel. An adjustable CEM connector will be used along with the calibration channel for testing the receiver. This will need to adjust the eye amplitude to specification values when measuring eye height/eye width. TP2 is a physical test point that will affect the eye opening due to trace length.

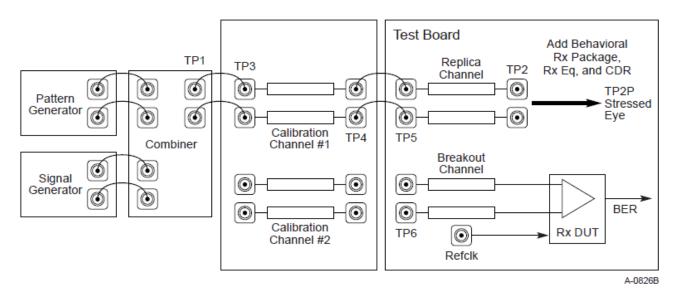

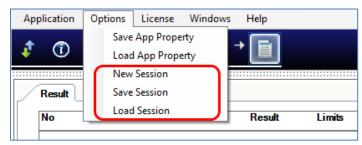

Figure 8-22 Rx Testboard Topology for 16.0 and 32.0 GT/s

FIGURE 7. RX CALIBRATION DIAGRAM FROM PHY TEST SPECIFICATION

For the Long Channel TP2 calibration, a PCI-SIG compliance load board (CLB) test fixture will be used for the host system board or a PCI-SIG compliance base board (CBB) test fixture for the add-in card. The board will be connected between the BERT noise generator output and the oscilloscope which will validate the test pattern of the signal and measure for stress tolerance to final stressed eye compliance. Post processing analysis of the signal is performed at the TP2P test point using the Seasim or SigTest application to simulate the stressed eye opening after applying Rx Behavioral package, Rx CTLE and DFE (if required). When calibration is completed, the GRL software will generate a test report detailing all results obtained from the calibration.

## 4.1 Set Up Automated Rx Calibration for TP3

Once pre-configuration has been completed from previous section, continue with the following calibration setup at TP3 (output of the BERT generator) using a GRL automation control enabled oscilloscope and Anritsu MP1900A BERT.

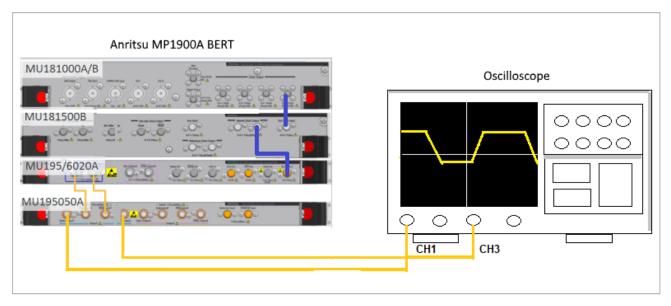

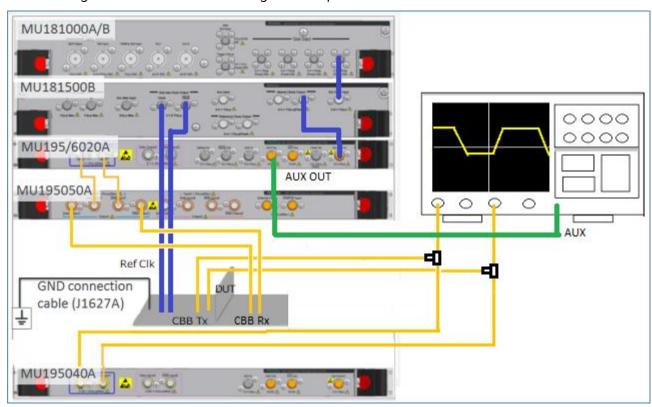

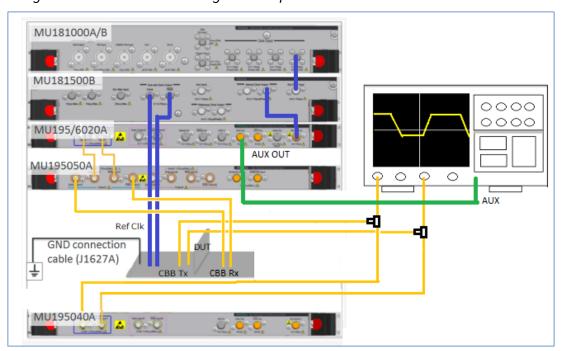

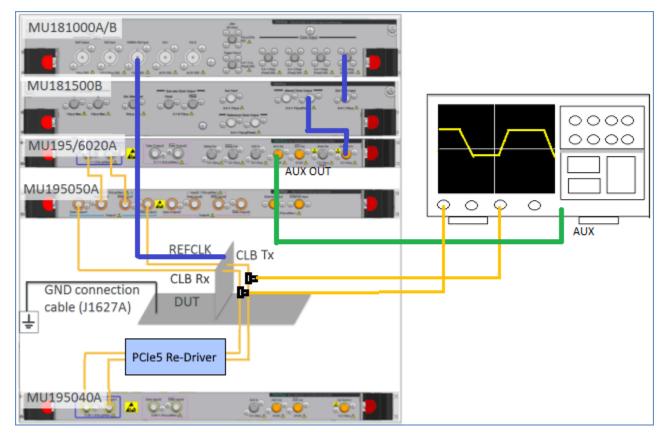

FIGURE 8. RECOMMENDED SETUP FOR TP3 RX CALIBRATION

- 1. Using a SMA-SMA short cable, connect the MU181000A/B clock output to the MU181500B Ext clock input.

- 2. Using a SMA-SMA short cable, connect the MU181500B jittered clock output to the MU195020A/MU196020A Ext clock input.

- 3. Using coaxial cables, connect the MU195020A/MU196020A data outputs to the MU195050A data inputs.

- 4. Using phase matched K-K coaxial cables, connect the MU195050A data outputs to Channels 1 and 3 on the oscilloscope.

### 4.1.1 TP3 Calibration Setup with Tektronix ATI Based Oscilloscope

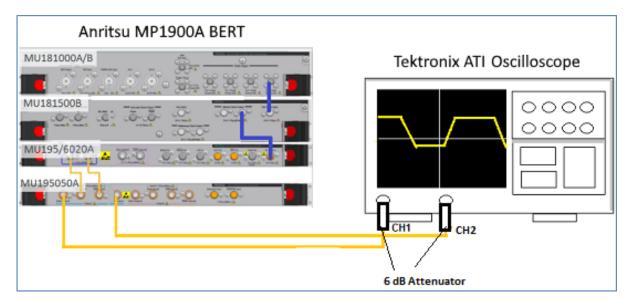

If the Tektronix ATI based oscilloscope is being used, proceed with the following TP3 calibration setup.

FIGURE 9. RECOMMENDED SETUP FOR TP3 RX CALIBRATION USING TEKTRONIX ATI SCOPE

Note: Make sure that the "Tektronix Scope Type" is set to **Dual ATI** in the Configurations page (see Section 4.6).

- 1. Follow back the same connections from step 1 to 3 in Section 4.1 above.

- 2. Then using phase matched K-K coaxial cables, connect the MU195050A data outputs to Channels 1 and 2 on the Tektronix ATI based oscilloscope through 6 dB attenuators.

## 4.2 Set Up Automated Rx Calibration for TP2

The next step is to calibrate the TP3-TP2 Channel (output of the Long Channel) with the following calibration setups using a GRL automation control enabled oscilloscope, Anritsu MP1900A BERT, and PCIe Gen 5 System Board or Add-In Card test fixtures. These calibration setups should also comply with insertion loss limits of 34 to 37 dB.

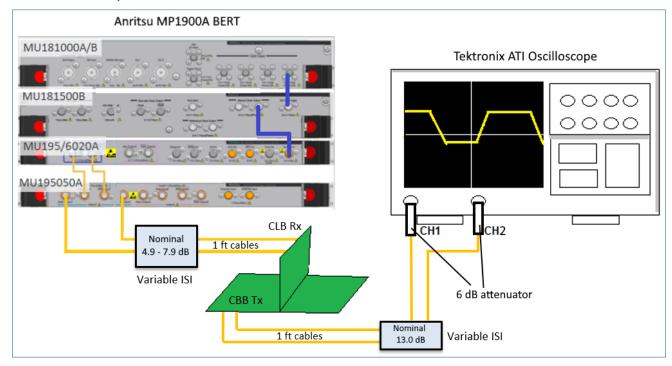

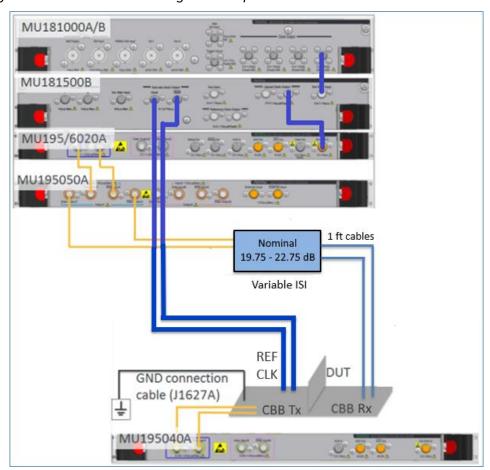

#### 4.2.1 Connect Equipment for System Board Calibration

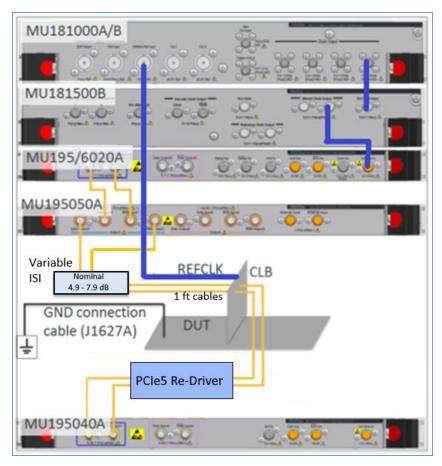

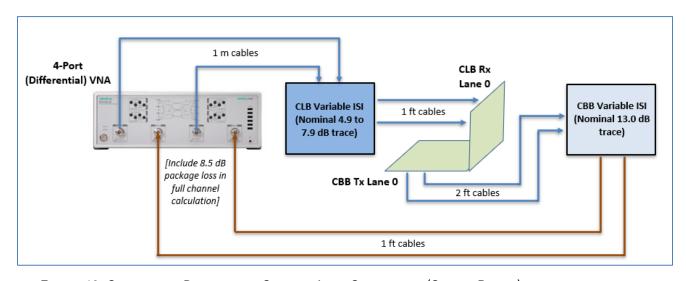

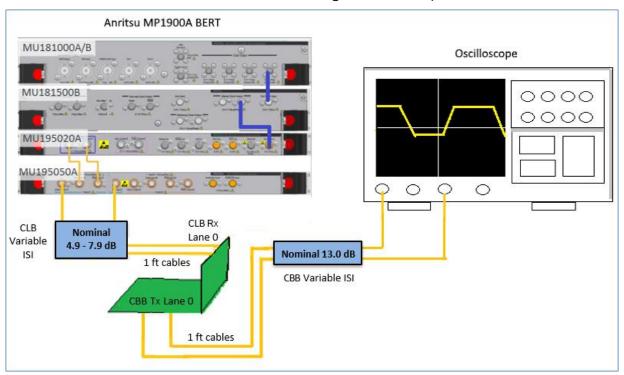

FIGURE 10. RECOMMENDED SETUP FOR TP2 LONG CHANNEL RX CALIBRATION (PCIE GEN 5 SYSTEM BOARD)

- Using back the same BERT connections from the TP3 calibration, disconnect the MU195050A data outputs from the oscilloscope channels.

- 2. Connect the MU195050A data outputs to Variable ISI (Nominal 4.9 7.9 dB).

- 3. Using 1 ft cables, connect between both the Variable ISI (Nominal 4.9 7.9 dB) and the CLB Rx Lane.

- 4. Using 1 ft cables, connect between both the CBB Tx Lane and Variable ISI (Nominal 13.0 dB).

- 5. Connect the Variable ISI (Nominal 13.0 dB) to Channels 1 and 3 on the oscilloscope.

#### 4.2.1.1 System Board Calibration Setup with Tektronix ATI Based Oscilloscope

If the Tektronix ATI based oscilloscope is being used, proceed with the following system board calibration setup.

FIGURE 11. RECOMMENDED SETUP FOR TP2 LONG CHANNEL RX CALIBRATION (PCIE GEN 5 SYSTEM BOARD) USING TEKTRONIX ATI SCOPE

Note: Make sure that the "Tektronix Scope Type" is set to **Dual ATI** in the Configurations page (see Section 4.6).

- 1. Follow back the same connections from step 1 to 4 in Section 4.2.1 above.

- 2. Then connect the Variable ISI (Nominal 13.0 dB) to Channels 1 and 2 on the Tektronix ATI based oscilloscope through 6 dB attenuators.

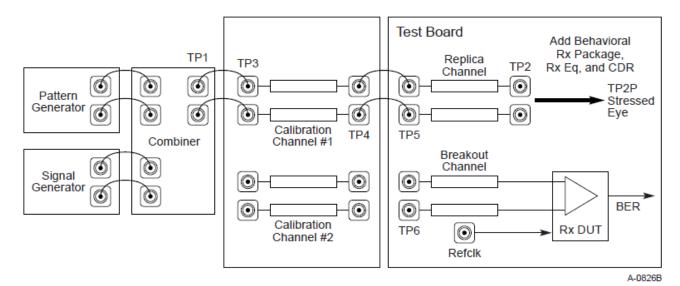

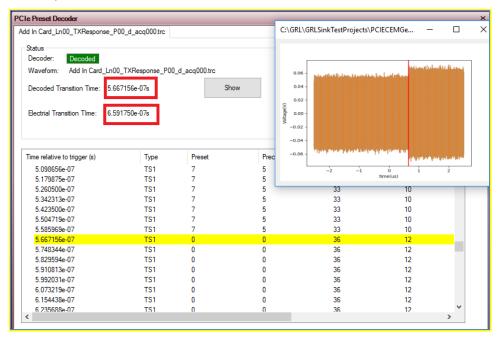

### 4.2.2 Connect Equipment for Add-In Card Calibration

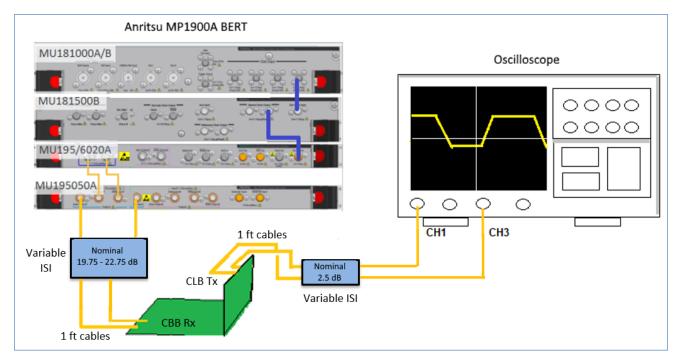

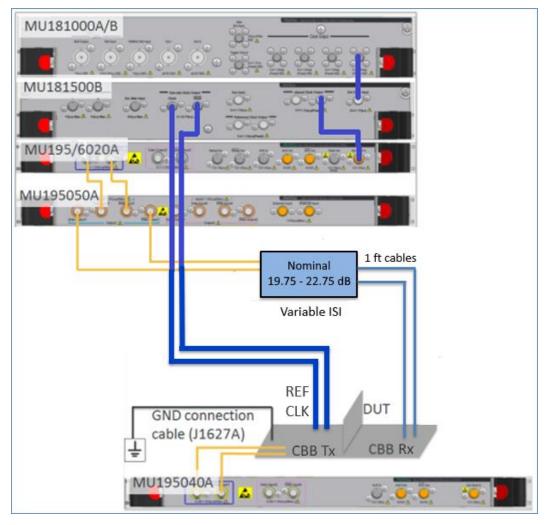

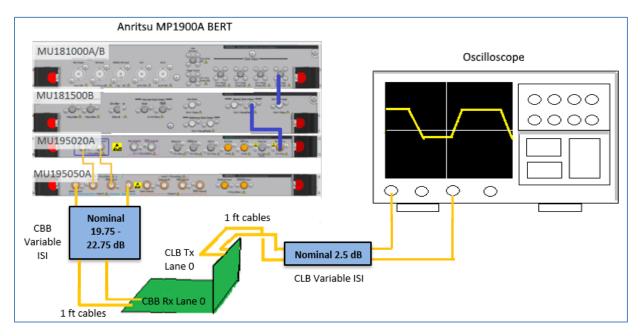

FIGURE 12. RECOMMENDED SETUP FOR TP2 LONG CHANNEL RX CALIBRATION (PCIE GEN 5 ADD-IN CARD)

- 1. Using back the same BERT connections from the TP3 calibration, disconnect the MU195050A data outputs from the oscilloscope channels.

- 2. Connect the MU195050A data outputs to Variable ISI (Nominal 19.75 22.75 dB).

- 3. Using 1 ft cables, connect between both the Variable ISI (Nominal 19.75 22.75 dB) and the CBB Rx Lane.

- 4. Using 1 ft cables, connect between both the CLB Tx Lane and Variable ISI (Nominal 2.5 dB).

- 5. Connect the Variable ISI (Nominal 2.5 dB) to Channels 1 and 3 on the oscilloscope.

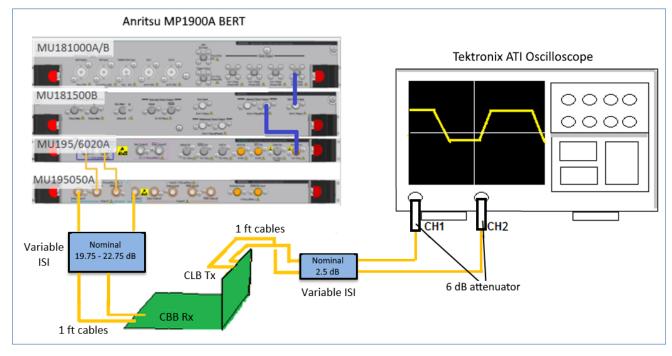

#### 4.2.2.1 Add-In Card Calibration Setup with Tektronix ATI Based Oscilloscope

If the Tektronix ATI based oscilloscope is being used, proceed with the following add-in card calibration setup.

FIGURE 13. RECOMMENDED SETUP FOR TP2 LONG CHANNEL RX CALIBRATION (PCIE GEN 5 ADD-IN CARD) USING TEKTRONIX ATI SCOPE

Note: Make sure that the "Tektronix Scope Type" is set to **Dual ATI** in the Configurations page (see Section 4.6).

- 1. Follow back the same connections from step 1 to 4 in Section 4.2.2 above.

- 2. Then connect the Variable ISI (Nominal 2.5 dB) to Channels 1 and 2 on the Tektronix ATI based oscilloscope through 6 dB attenuators.

#### 4.3 Set Measurement Conditions

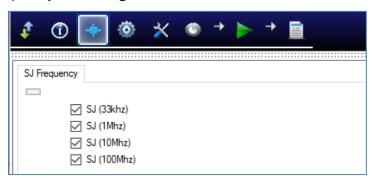

Select from the GRL PCIe CEM 5.0 Rx Test Application menu to access the **Conditions** page to set the conditions for calibration and testing. The GRL software will perform calibration and testing for selected defined SJ frequencies.

Recommended procedure:

• *Step 1*: When calibrating, select all conditions that may be used for testing, and perform the calibration.

• Step 2: Once calibration is completed and ready for testing, re-select the necessary test conditions. For example, if required to test for a single SJ frequency, then select only the required SJ frequency for testing.

FIGURE 14. SELECT TEST CONDITION

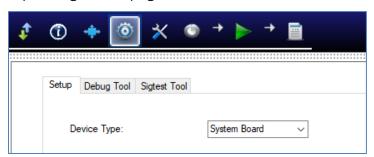

# 4.4 Set Up Calibration Requirements

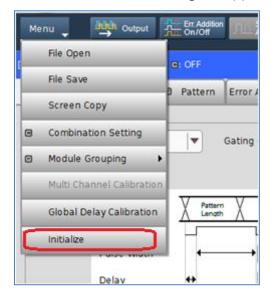

After setting up the physical equipment, select from the GRL PCIe CEM 5.0 Rx Test Application menu to access the Setup Configuration page.

FIGURE 15. SET UP CALIBRATION REQUIREMENTS

### 4.4.1 Setup Tab

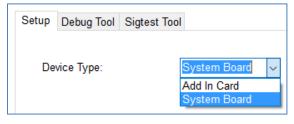

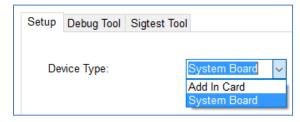

Select to use a compliant PCIe System Board or Add-In Card as the calibration device.

FIGURE 16. SELECT DEVICE FOR CALIBRATION

#### 4.5 Select PCIe CEM 5.0 Rx Calibration

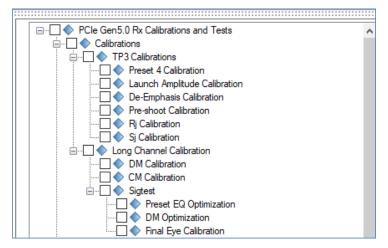

After selecting the device to be calibrated, access the **Select Tests** page on the left of the screen to select the available PCIe CEM 5.0 based receiver calibration to be performed. Select the check box(s) of the desired Rx calibration.

FIGURE 17. SELECT RX CALIBRATION

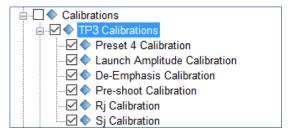

#### 4.5.1 Select to Perform TP3 Calibration

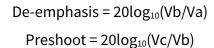

Under 'TP3 Calibrations', select to calibrate for initial Tx equalization preset, BERT de-emphasis and pre-shoot (which form a linear curve fit), launch amplitude, random jitter (RJ), and sinusoidal jitter (SJ) (for PCIe Gen 5 frequencies as per PCIe CEM 5.0 Rx specs and forms a linear curve fit for each SJ frequency).

The GRL software will automatically run the selected calibration when initiated.

FIGURE 18. SELECT TP3 CALIBRATION

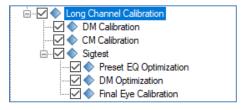

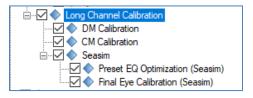

#### 4.5.2 Select to Perform Long Channel TP2 Calibration

Under 'Long Channel Calibration', select to calibrate for differential mode (DM), common mode (CM), and SigTest or Seasim eye calibration parameters to achieve calibrated eye height and width to produce a final stressed eye diagram.

Note that the list for SigTest eye calibration (for preset equalization (EQ) optimization, DM optimization, and final eye calibration) or Seasim eye calibration (for preset EQ optimization and final eye calibration) can be toggled using the **Configurations** page "Eye Calibration Method" parameter. See Section 4.6 for more details.

The GRL software will automatically run the selected calibration when initiated.

FIGURE 19. SELECT LONG CHANNEL TP2 CALIBRATION (WITH SIGTEST)

FIGURE 20. SELECT LONG CHANNEL TP2 CALIBRATION (WITH SEASIM)

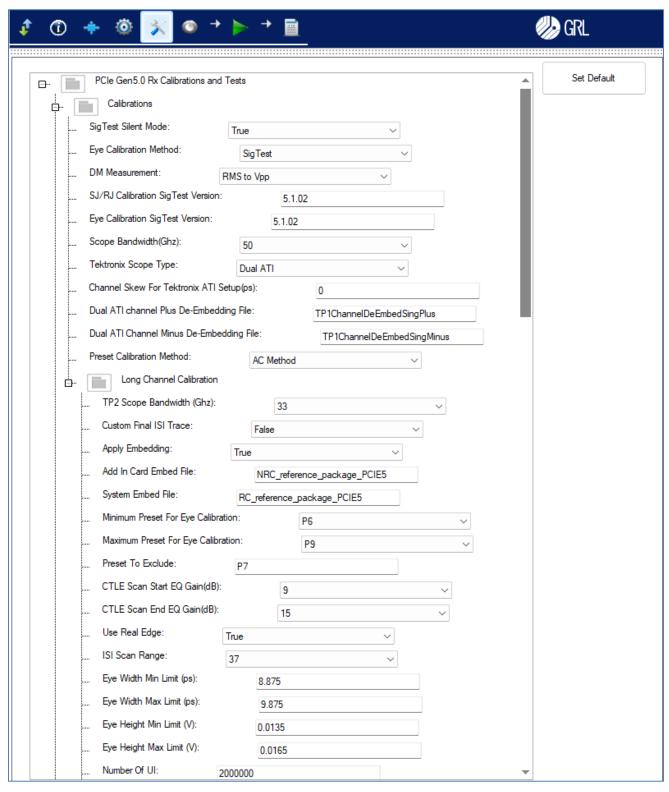

# 4.6 Configure Calibration Parameters

After selecting the desired calibration, select from the menu to access the Configurations page. Set the required parameters for calibration as described below.

To return all parameters to their default values, select the 'Set Default' button.

FIGURE 21. CALIBRATION PARAMETERS CONFIGURATION PAGE

TABLE 4. CALIBRATION PARAMETERS DESCRIPTION

| Parameter                                          | Description                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SigTest Silent Mode                                | Select 'True' to enable running the SigTest in silent mode during calibration.                                                                                                                                                                                                                                                              |

| Eye Calibration Method                             | Select either the SigTest or Seasim application to be used for final stressed eye calibration and post processing signal quality testing. Make sure that the SigTest or Seasim application is already installed in the test controller system. Note this SigTest or Seasim selection will cause the calibration list to change accordingly. |

| DM Measurement                                     | Select the unit for measuring differential mode (DM).                                                                                                                                                                                                                                                                                       |

| SJ/RJ Calibration SigTest<br>Version               | If the SigTest method is selected to be applied during calibration of SJ or RJ, enter the Version number of the SigTest to be used. Make sure that the SigTest application is already installed in the test controller system.                                                                                                              |

| Eye Calibration SigTest<br>Version                 | If the SigTest method is selected to be applied during eye calibration, enter the Version number of the SigTest to be used. Make sure that the SigTest application is already installed in the test controller system.                                                                                                                      |

| Scope Bandwidth (GHz)                              | Select the appropriate bandwidth of the Scope being used for measurements.                                                                                                                                                                                                                                                                  |

| Tektronix Scope Type                               | If the Tektronix Scope is to be used for measurements, select either the Single-shot based Scope or the Tektronix' owned Dual Asynchronous Time Interleaving (Dual ATI) based Scope.                                                                                                                                                        |

| Channel Skew For<br>Tektronix ATI Setup (ps)       | If the Tektronix ATI based Scope is to be used for measurements, enter the channel skew or timing to perform alignment of the Scope channels.                                                                                                                                                                                               |

| Dual ATI Channel Plus /<br>Minus De-Embedding File | If the Tektronix ATI based Scope is to be used for measurements, specify the file name for de-embedding on the respective Scope channel.                                                                                                                                                                                                    |

| Preset Calibration<br>Method                       | Select the "AC Method" or "DC Method" to be used for preset calibration.                                                                                                                                                                                                                                                                    |

| TP2 Scope Bandwidth (GHz)                          | Select the bandwidth of the Scope to be used for TP2 measurements.                                                                                                                                                                                                                                                                          |

| Custom Final ISI Trace                             | Select 'True' to enable generating custom ISI trace for the final ISI calibration.                                                                                                                                                                                                                                                          |

| Apply Embedding                                    | Select 'True' to embed the add-in card or system board DUT for calibration.                                                                                                                                                                                                                                                                 |

| Add-In Card / System<br>Embed File                 | Specify the file name for the embedded add-in card or system board.                                                                                                                                                                                                                                                                         |

| Minimum & Maximum<br>Preset for Eye<br>Calibration | Select the range of presets to be applied for stressed eye calibration.                                                                                                                                                                                                                                                                     |

| Preset to Exclude                                  | Specify the preset that is not used for calibration.                                                                                                                                                                                                                                                                                        |

| CTLE Scan Start & End EQ<br>Gain (dB)     | Select the optimized CTLE Equalization Gain setting index to be used based on the CTLE model to measure the Eye area.                                                                        |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Use Real Edge                             | Select 'True' to use Real Edge connection for test setup on the Oscilloscope.  Note: This setting is only applicable for the Keysight Scope.                                                 |

| ISI Scan Range                            | Select the scan range during ISI calibration.                                                                                                                                                |

| Eye Width & Eye Height<br>Min / Max Limit | Enter the limits for maximum and minimum eye calibration values.                                                                                                                             |

| Number Of UI                              | Enter the number of unit interval (UI) samples to acquire during calibration.                                                                                                                |

| Final Eye Convergence                     | Select either a Strict or Loose method to be applied in the calculation for the final calibrated eye.                                                                                        |

| Brute Force Method                        | Select 'True' to enable DM Optimization SJ to continue scanning until all SJ ranges are included. The GRL-PCIE5-CEM-RXA software will then select the DM with Eye Height closest to 0.015 V. |

| If the SigTest method is selected:        |                                                                                                                                                                                              |

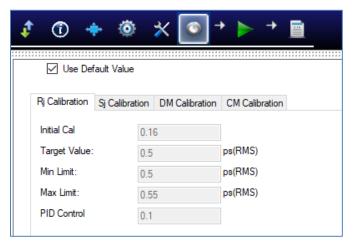

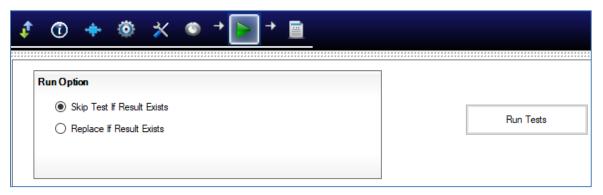

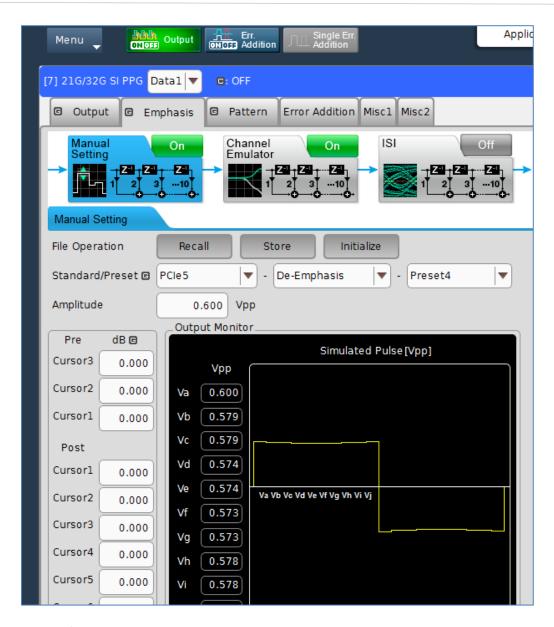

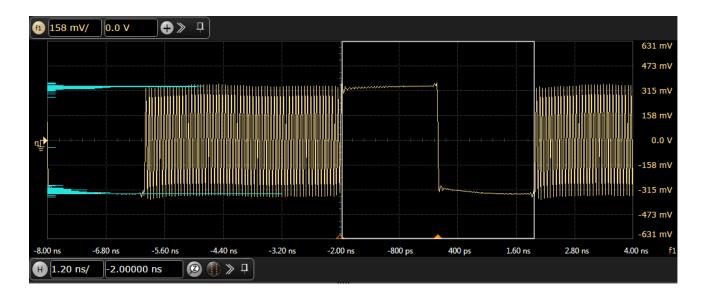

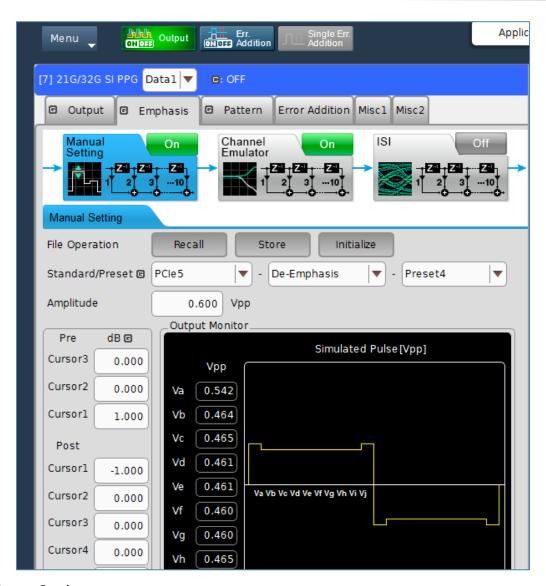

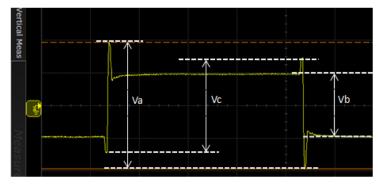

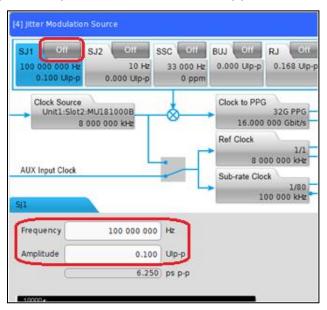

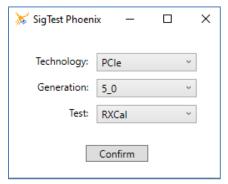

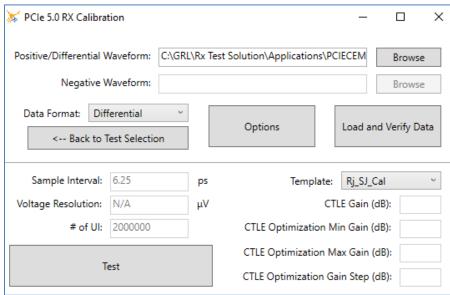

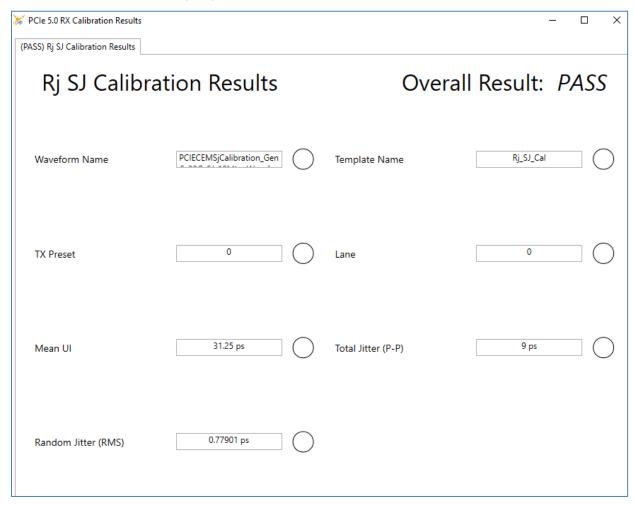

| Parallel SigTest Run                      | Select 'True' to enable running the SigTest in parallel mode with the Long Channel TP2 calibration.                                                                                          |