# **Granite River Labs**

PCI Express® 4.0 Base Specification (Version 1.0)

Receiver Test Method of Implementation (MOI)

for Anritsu 16Gbps Physical Layer Test Suite

Using Anritsu MP1800A/MP1900A BERT,

High Performance Real-time Oscilloscope,

and GRL-PCIE4-BASE-RXA Calibration and Test Software

Published on 22 September 2022

#### **DISCLAIMER**

This document is provided "as is" with no warranties whatsoever, including any warranty of merchantability, no infringement, fitness for any particular purpose, or any warranty otherwise arising out of any proposal, specification, or sample. The GRL disclaims all liability for infringement of proprietary rights, relating to use of information in this specification. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted herein.

All product names are trademarks, registered trademarks, or service marks of their respective owners.

Copyright © 2022 Granite River Labs. All rights reserved.

### **TABLE OF CONTENTS**

| 1 | IN.        | NTRODUCTION                                                                                   | 8  |

|---|------------|-----------------------------------------------------------------------------------------------|----|

|   | 1.1        | GLOSSARY                                                                                      | 9  |

|   | 1.2        | REFERENCE DOCUMENTS                                                                           | 9  |

|   | 1.3        | ACKNOWLEDGEMENTS                                                                              | 10 |

|   | 1.4        | FEEDBACK                                                                                      | 10 |

| 2 | RE         | ESOURCE REQUIREMENTS                                                                          | 11 |

|   | 2.1        | EQUIPMENT REQUIREMENTS                                                                        | 11 |

|   | 2.2        | SOFTWARE REQUIREMENTS                                                                         | 13 |

| 3 | SE         | ETTING UP GRL-PCIE4-BASE-RXA SOFTWARE                                                         | 14 |

|   | 3.1        | DOWNLOAD GRL-PCIE4-BASE-RXA SOFTWARE                                                          | 14 |

|   | 3.2        |                                                                                               |    |

|   | 3.2        | 2.1 Connection Configuration on the Scope or Controller PC OS                                 | 16 |

|   | 3.3        |                                                                                               |    |

|   |            | <ul><li>3.1 Enter Test Session Information</li></ul>                                          |    |

|   |            | 3.3 Setup Configuration                                                                       |    |

| 4 | CA         | ALIBRATING USING GRL-PCIE4-BASE-RXA SOFTWARE                                                  | 24 |

|   | 4.1        | CALIBRATION FOR TP1 (OUTPUT OF BERT GENERATOR)                                                | 25 |

|   | 4.1        |                                                                                               |    |

|   |            | 1.2 Setup for TP1 Calibration (Using MP1900A BERT)                                            |    |

|   |            | 1.3 Select Calibration                                                                        |    |

|   | 4.1<br>4.1 | <ul><li>1.4 Configure Calibration Parameters</li><li>1.5 Run Calibration at TP1</li></ul>     |    |

|   | 4.2        | CALIBRATION FOR TP2 (OUTPUT OF LONG CHANNEL)                                                  | 31 |

|   |            | 2.1 Setup for TP2 Calibration (Using MP1800A BERT)                                            |    |

|   |            | 2.2 Setup for TP2 Calibration (Using MP1900A BERT)                                            |    |

|   |            | 2.3 Run Calibration Steps at TP2                                                              |    |

|   |            | 2.4 Set Up SigTest for Final Stressed Eye Calibration                                         |    |

| 5 | TE         | ESTING USING GRL-PCIE4-BASE-RXA SOFTWARE                                                      | 39 |

|   | 5.1        | RECEIVER DUT COMPLIANCE TEST SETUP                                                            |    |

|   | 5.1<br>5.1 | <ul><li>1.1 Test Setup Using MP1800A BERT</li><li>1.2 Test Setup Using MP1900A BERT</li></ul> |    |

|   |            | 1.3 Receiver Compliance Tests                                                                 |    |

|   |            | ·                                                                                             |    |

|    | 5.1<br>5.1<br>5.1 | .5          | Receiver Margin Tests                                                                | 42  |

|----|-------------------|-------------|--------------------------------------------------------------------------------------|-----|

|    |                   |             | Configure Receiver Test Parameters                                                   |     |

| _  | 5.2               |             |                                                                                      |     |

| 6  | IN                | TER         | PRETING TEST REPORT                                                                  | 45  |

|    | 6.1               | DU          | T Information                                                                        | 45  |

|    | 6.2               | SuM         | IMARY TABLE                                                                          | 46  |

|    | 6.3               | CAL         | IBRATION DATA RESULTS                                                                | 47  |

|    | 6.4               | Сом         | IPLIANCE TEST RESULTS                                                                | 48  |

|    | 6.5               | MAF         | RGIN TEST RESULTS                                                                    | 49  |

| 7  | SA                | VIN         | G AND LOADING TEST SESSIONS                                                          | 50  |

| 8  | AP                | PEN         | NDIX A: METHOD OF IMPLEMENTATION (MOI) USING AUTOMATION                              | N51 |

|    | 8.1               | PER         | FORM CALIBRATION AT TP1                                                              |     |

|    | 8.1               |             | Pre-shoot Calibration                                                                |     |

|    | 8.1               |             | De-emphasis Calibration                                                              |     |

|    | 8.1               |             | Launch Amplitude Calibration                                                         |     |

|    | 8.1<br>8.1        |             | RJ CalibrationSJ Calibration                                                         |     |

|    | 8.1               |             | SJ Tone (33KHz SSC) Calibration                                                      |     |

|    | 8.2               |             | FORM CALIBRATION AT TP2                                                              |     |

|    | 8.2               |             | Insertion Loss Calibration (Applicable only if CTS version '0.7' is being used as to |     |

|    | me                |             | ement reference method)                                                              |     |

|    | 8.2               |             | ISI Calibration (CEM Connector Channel + Replica Channel) [Applicable only if        |     |

|    |                   |             | '1.0' is being used as the measurement reference method AND supported ISI Gen        |     |

|    |                   |             | Cle ISI Board or Artek is used.]                                                     |     |

|    | 8.2               |             | Common Mode (CM) Sinusoidal Interference Calibration                                 |     |

|    | 8.2               |             | Differential Mode (DM) Sinusoidal Interference Calibration                           |     |

|    | 8.2<br>8.2        |             | Optimized Preset/Final ISI CalibrationStress Jitter Voltage Eye Calibration          |     |

|    | 8.2               |             | DM Optimization and Final Eye Calibration Using SigTest                              |     |

| 9  |                   |             | NDIX B: ARTEK CLE MODEL SERIES INSTALLATION                                          | 60  |

|    |                   |             |                                                                                      |     |

| 1( |                   |             | ENDIX C: RECEIVER RETURN LOSS                                                        | 63  |

| 1: |                   |             | ENDIX D: CONNECTING KEYSIGHT OSCILLOSCOPE TO PC                                      | 65  |

| 1  | 2 A               | <b>NPPI</b> | ENDIX E: CONNECTING TEKTRONIX OSCILLOSCOPE TO PC                                     | 67  |

### 13 APPENDIX F: SCOPE AND CABLE DE-SKEW

69

# **List of Figures**

| Figure 1. Select and Launch GRL Framework                                              | 15 |

|----------------------------------------------------------------------------------------|----|

| Figure 2. Start PCIe 4.0 Base Rx Test Application                                      | 15 |

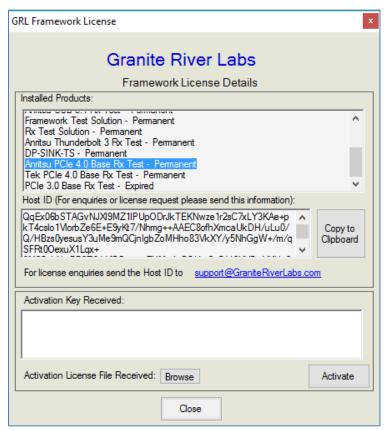

| Figure 3. See License Details                                                          | 15 |

| Figure 4. Check License for Installed Applications                                     | 15 |

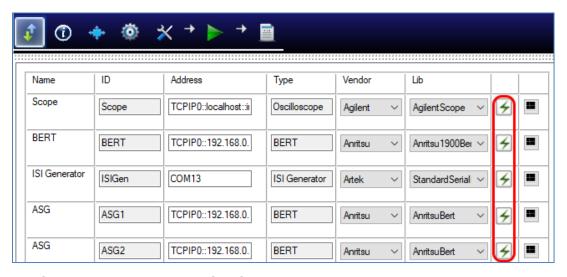

| Figure 5. Connect Instruments with GRL Software                                        | 17 |

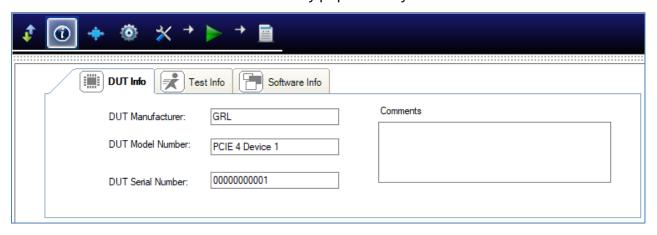

| Figure 6. Session Info Page                                                            | 18 |

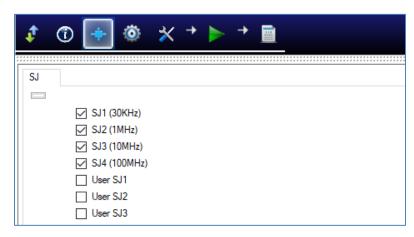

| Figure 7. Select SJ Frequencies                                                        | 19 |

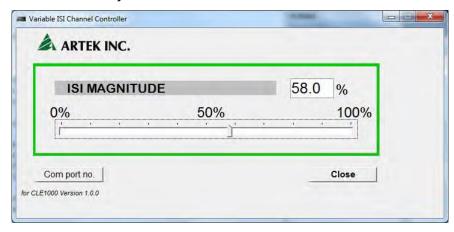

| Figure 8. ISI Generator Setup                                                          | 19 |

| Figure 9. BER Loopback Test Method                                                     | 20 |

| Figure 10. User SJ Frequencies Setting                                                 | 20 |

| Figure 11. Loopback Mode Setup                                                         | 21 |

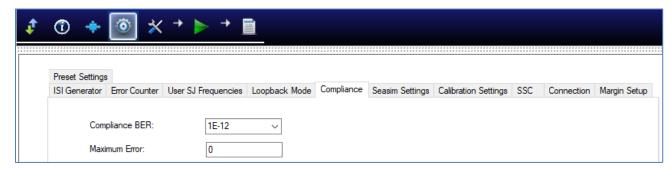

| Figure 12. Compliance BER and Maximum Errors Setup                                     | 21 |

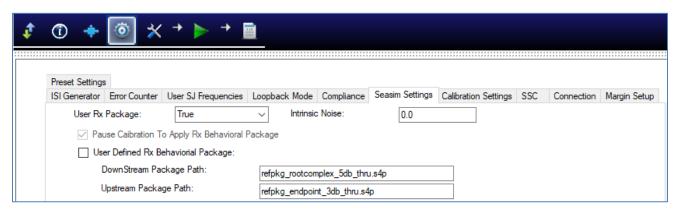

| Figure 13. Seasim Settings                                                             | 22 |

| Figure 14. DM and CM Calibration Settings                                              | 22 |

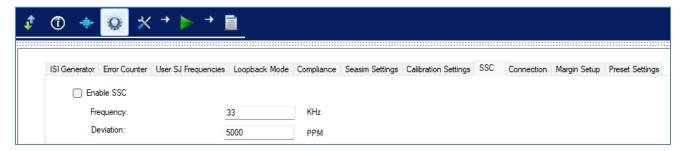

| Figure 15. SSC Setup                                                                   | 22 |

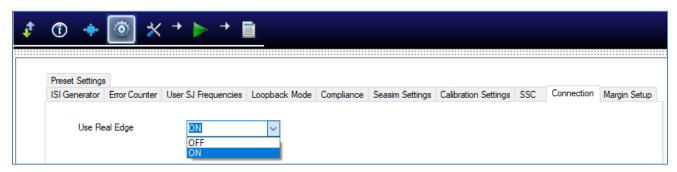

| Figure 16. Connection Setup                                                            | 23 |

| Figure 17. Margin Search Parameters Setup                                              | 23 |

| Figure 18. Preset Settings                                                             | 23 |

| Figure 19. Rx Calibration Block Diagram from the PCIe 4.0 Base Specification           | 24 |

| Figure 20. Rx Calibration/Test Schematic Overview from the PCIe 4.0 Base Specification | 25 |

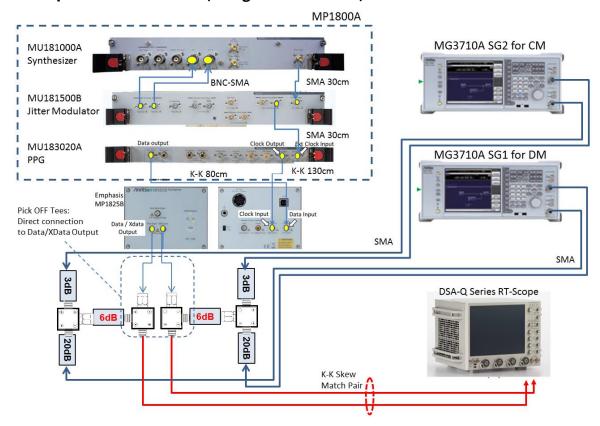

| Figure 21. Typical Setup for TP1 Calibration (Using MP1800A BERT)                      | 25 |

| Figure 22. Typical Setup for TP1 Calibration (Using MP1900A BERT)                      | 26 |

| Figure 23. Calibration Selection                                                       | 28 |

| Figure 24. Calibration Parameters Configuration Page                                   | 29 |

| Figure 25. Run Tests                                                                   | 30 |

| Figure 26. TP1 Connection Diagram Dialog                                               | 31 |

| Figure 27. Typical Setup for TP2 Calibration (Using MP1800A BERT)                      | 32 |

| Figure 28. Calibrated IL Example Using GRL-PCIE4-BASE-RXA                              | 33 |

| Figure 29. Typical Setup for TP2 Calibration (Using MP1900A BERT)                      | 34 |

| Figure 30. Final Calibrated Stressed Eye Diagram Example                               | 35 |

| Figure 31. Typical Receiver DUT Test Setup (Using MP1800A BERT)                        | 40 |

| Figure 32. Typical Receiver DUT Test Setup (Using MP1900A BERT)                        | 41 |

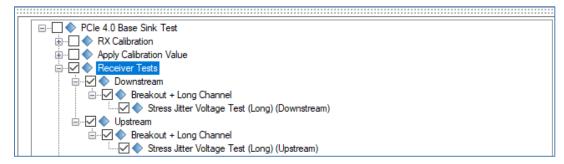

| Figure 33. Selecting Receiver Compliance Tests                                         | 42 |

|                                                                                        |    |

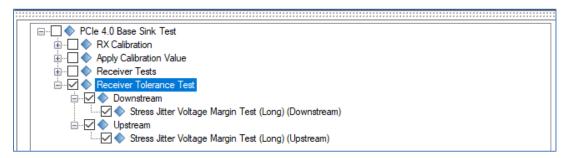

| Figure 34. Selecting Receiver Margin Tests                  | 42 |

|-------------------------------------------------------------|----|

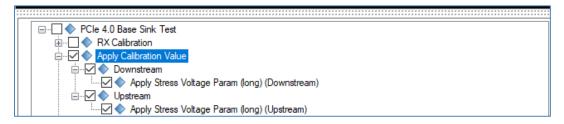

| Figure 35. Selecting To Apply Calibration Values            | 42 |

| Figure 36. Receiver Test Parameters Configuration Page      | 43 |

| Figure 37. Select BER Loopback Test Method                  | 44 |

| Figure 38. Set Up Loopback Test                             | 44 |

| Figure 39. Set BER/Error Limits                             | 44 |

| Figure 40. Report Results Page                              | 45 |

| Figure 41. DUT Information                                  | 45 |

| Figure 42. Summary Table                                    |    |

| Figure 43. Calibration Results Example                      | 47 |

| Figure 44. Compliance Test Results Example                  | 48 |

| Figure 45. Margin Test Results Example                      | 49 |

| Figure 46. Saving and Loading Calibration and Test Sessions | 50 |

| Figure 47. De-emphasis Calibration Caltable Graph           | 52 |

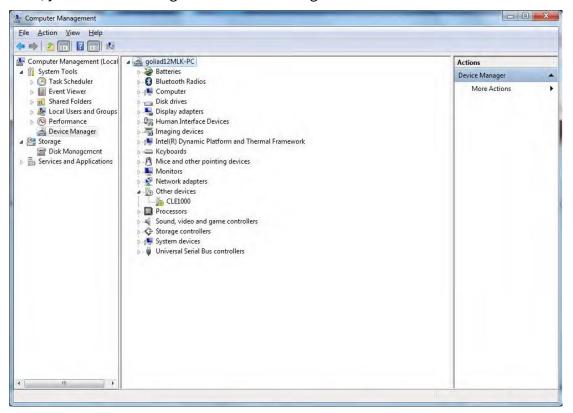

| Figure 48. Device Manager Window                            | 60 |

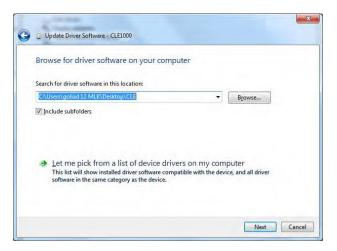

| Figure 49. Update Driver Window                             | 61 |

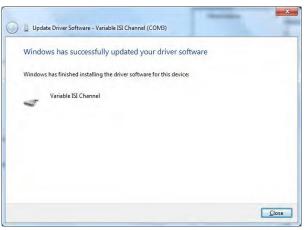

| Figure 50. Windows Security Window And Confirmation Window  | 61 |

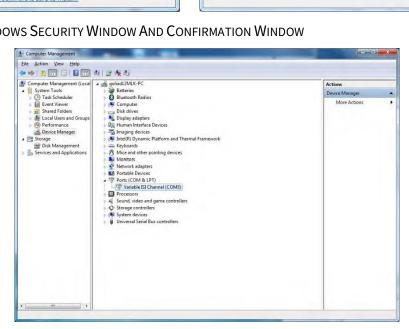

| Figure 51. Device Manager Window After Installation         | 61 |

| Figure 52. CLE Series GUI                                   | 62 |

| FIGURE 53. Differential Mode Return Loss Mask               | 63 |

| FIGURE 54. Common Mode Return Loss Mask                     | 64 |

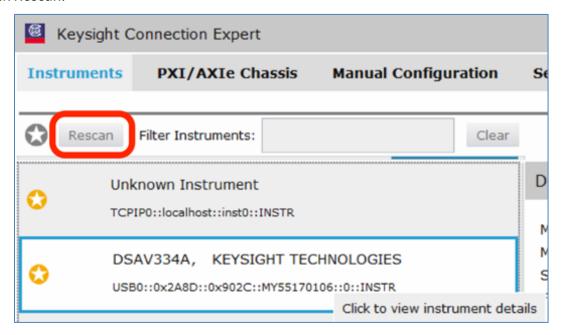

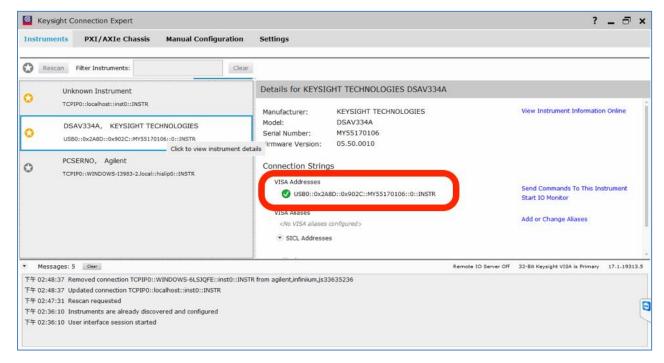

| Figure 55. Keysight Connection Expert                       | 65 |

| Figure 56. Oscilloscope's VISA Address                      | 66 |

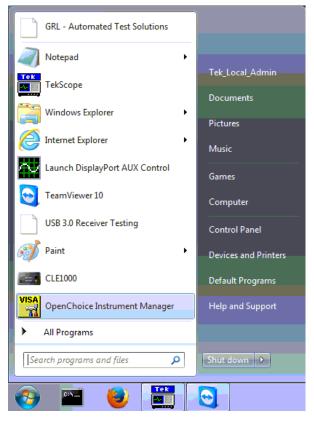

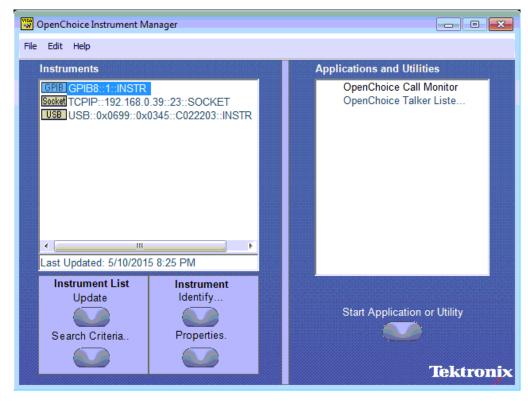

| Figure 57. OpenChoice Instrument Manager In Start Menu      | 67 |

| Figure 58. OpenChoice Instrument Manager Menu               | 68 |

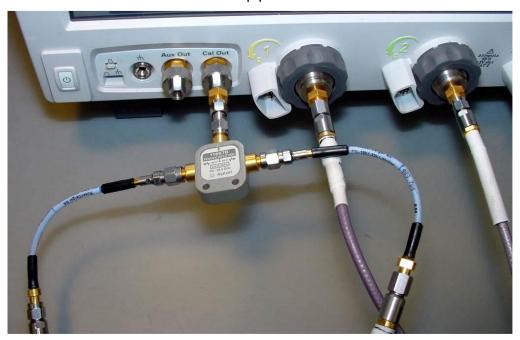

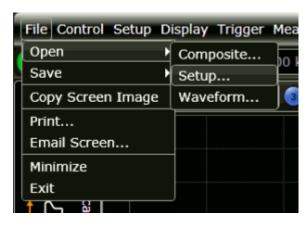

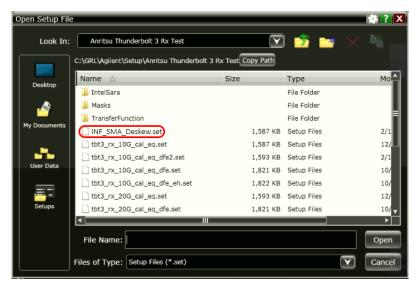

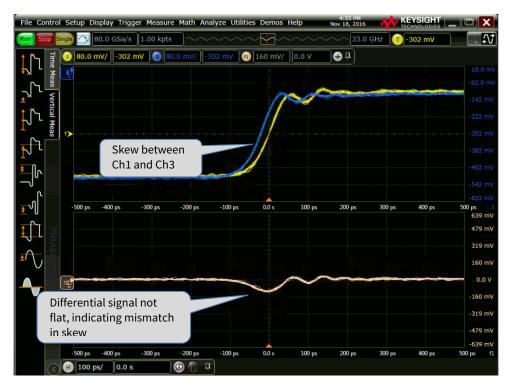

| Figure 59. Scope Deskew Setup                               | 69 |

| Figure 60. Open Scope De-skew Setup File Window             | 70 |

| Figure 61. Scope De-skew Setup File Example                 | 70 |

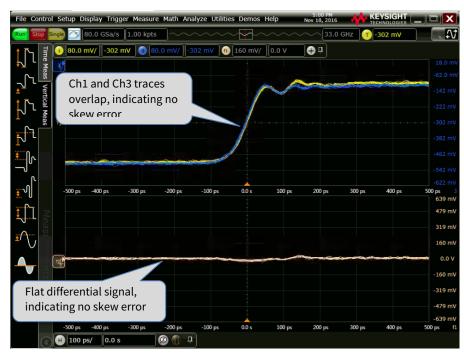

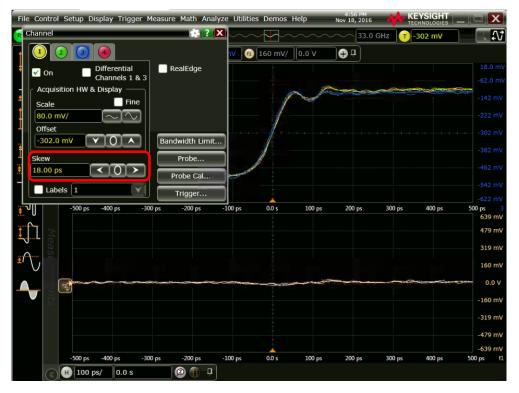

| Figure 62. Scope De-skew Oscilloscope Display               | 71 |

| Figure 63. Scope De-skew Oscilloscope Display De-skewed     | 72 |

| Figure 64. Scope De-skew Process – Open Channel Window      | 72 |

| Figure 65. Scope De-skew Process – Adjust Skew              | 72 |

# 1 Introduction

This User Guide & MOI describes the procedures for receiver (Rx) calibration and jitter tolerance testing based on the PCIe Base 4.0 (ASIC) Specification (for 16 GT/s), using the GRL-PCIE4-BASE-RXA PCIe 4.0 Base Specification Receiver Calibration and Test Software to automate the Anritsu BERT Model (MP1800A/MP1900A) and a high performance real-time oscilloscope to calibrate the stressed eye opening and test receiver conformance and jitter tolerance. The GRL-PCIE4-BASE-RXA software uses Seasim statistical data eye simulator to establish the calibrated test channel DDJ. The final calibrated eye diagram uses both Seasim and SigTest software to achieve the final stressed eye calibration.

The BERT and appropriate accessories provide the necessary test patterns with jitter, ISI, and crosstalk. Additionally, the BERT is used to add the required transmitter (Tx) equalization. The receiver jitter tolerance test includes various Differential Mode Sinusoidal Interference, minimum transmitter voltage amplitude, and jitter which includes random jitter and a sinusoidal periodic jitter component that is swept across specific frequency intervals.

Once the stressed receiver eye opening has been calibrated, the receiver jitter tolerance and margin testing can then be performed on the device under test (DUT). The BERT is used to transmit a modified compliance pattern to the receiver DUT and monitors that the loopback pattern conforms to a Bit Error Ratio (BER) that is less than 10<sup>-12</sup> with a confidence level of 95%.

In summary, this User Guide & MOI basically describes using the GRL-PCIE4-BASE-RXA software to:

- 1. Calibrate the stressed eye at the receiver of the DUT.

- This includes calibrating Voltage Swing, Random Jitter (RJ), Sinusoidal Jitter (SJ),

Differential Noise, Common Mode Noise, Tx Equalization and Eye Height & Width.

- 2. Test the receiver using Bit Error Ratio (BER) as a metric. The receiver path is tested with worst case eye to ensure a BER of less than 10<sup>-12</sup> can be achieved.

Note: Important information detailing method of implementation using automation, oscilloscope and cable calibration, as well as other setup information are included in Appendixes of this document. It is highly recommended to thoroughly review these information prior to performing any testing or data collection.

The GRL-PCIE4-BASE-RXA software is designed to work with the Anritsu BERT as a signal source and error detector for automation of the PCIe Gen 4.0 Base Receiver calibration and testing. Details on how to set up and configure the GRL software are provided in this document.

## 1.1 Glossary

SJ Sinusoidal Jitter

ISI Inter Symbol Interference

RJ Random Jitter

CTLE Continuous Time Linear Equalization

DFE Decision Feedback Equalization

CDR Clock / Data Recovery

BER Bit Error Rate

BERT Bit Error Rate Tester

EH Eye Height

EW Eye Width

DPP Digital Pre-emphasis Processor

Upstream Reference to Host Test Setup (Calibrated with Device Channel)

Downstream Reference to Device Test Setup (Calibrated with Host Channel)

DUT Device Under Test

#### 1.2 Reference Documents

- [1] PCI Express<sup>®</sup> Base Specification Rev. 4.0; Version 0.7; March, 2016

- [2] PCI Express<sup>®</sup> Base Specification Rev. 4.0; Version 1.0; September 27, 2017

- [3] PCI Express Card Electromechanical Specification, Revision 4.0

- [4] PCI Express to PCI/PCI-X Bridge Specification, Revision 1.0

- [5] PCI Express Mini Card Electromechanical Specification, Revision 2.1

- [6] PCI Express OCuLink Specification, Revision 1.0

- [7] PCI Express M.2 Specification, Revision 1.1

- [8] PCI Express External Cabling Specification, Revision 2.0

- [9] PCI Express ExpressModule Electromechanical Specification, Revision 1.0

- [10] PCI-X Addendum to the PCI Local Bus Specification, Revision 2.0

- [11] PCI Hot-Plug Specification, Revision 1.1

- [12] PCI Standard Hot-Plug Controller and Subsystem Specification, Revision 1.0

- [13] PCI Code and ID Assignment Specification, Revision 1.9 (or later)

- [14] PCI Firmware Specification, Revision 3.2

- [15] Advanced Configuration and Power Interface Specification, Revision 6.2

- [16] Unified Extensible Firmware Interface (UEFI) Specification Version 2.7 Errata A

- [17] Guidelines for 64-bit Global Identifier (EUI-64) Registration Authority

- [18] Multi-Root I/O Virtualization and Sharing Specification, Revision 1.0

The most current versions of above documents and ECNs are available to PCI-SIG Working Group members at: <a href="http://www.pcisig.com/specifications/pciexpress/">http://www.pcisig.com/specifications/pciexpress/</a>

# 1.3 Acknowledgements

The following individuals and their companies have contributed to the creation and maintenance of this document:

Darren Gray (Author) – Granite River Labs (GRL), Inc.

Kaushal Patel (Editor) – Granite River Labs (GRL), Inc.

Swee Guan Chua [SG] (Contributor) – Granite River Labs (GRL), Inc.

Chin Hun Yaep [CH] (Contributor) – Granite River Labs (GRL), Inc.

Marc Wells (Contributor) – Granite River Labs (GRL), Inc.

Ong Gaik Pheng (Editor) – Granite River Labs (GRL), Inc.

#### 1.4 Feedback

Please send feedback on this document to info@graniteriverlabs.com.

# 2 Resource Requirements

# 2.1 Equipment Requirements

TABLE 1. EQUIPMENT REQUIREMENTS – SYSTEMS AND ACCESSORIES

| Equipment                          | Qty. | Description                                                                                                                                                   | Key Specification Requirement                                                                                                                       |

|------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Keysight/Tektronix<br>Oscilloscope | 1    | High Performance Real-time<br>Oscilloscope [a]                                                                                                                | ≥ 32 GHz bandwidth with Windows 7+ OS  [b]                                                                                                          |

| Anritsu MP1800A/<br>MP1900A BERT   | 1    | <ul> <li>modules:</li> <li>MU181000A/B 12.5GHz Sy</li> <li>MU181500B Jitter Modula</li> <li>MU183020A 28G/32Gbit/s<br/>022 [1-channel or 2-channel</li> </ul> | stion Source SI Pulse Pattern Generator (Option 012 or nel], 030 or 031) SI High Sensitivity Error Detector (Option                                 |

|                                    | 1    | 64.2G bit/s or 64.2G baud                                                                                                                                     | ynthesizer ation Source s SI Pulse Pattern Generator, or MU196020A PAM4 Pulse Pattern Generator <sup>[c]</sup> t/s Error Detector, or MU196040B 58G |

| Anritsu MP1825B                    | 1    | De-Emphasis Signal Converter                                                                                                                                  | Option: 002<br>Applies for MP1800A BERT only                                                                                                        |

| Anritsu MG3710A                    | 2    | Vector Signal Generator                                                                                                                                       | Option: 002, 029, 036, 041, 066, 071<br>Applies for MP1800A BERT only                                                                               |

| ISI Generator                      | 1    | PCIe-4 Base Spec compliant Fixed                                                                                                                              | l or Variable ISI Channel <sup>[d]</sup>                                                                                                            |

| Anritsu K241C                      | 2    | Power Splitter                                                                                                                                                | Applies for MP1800A BERT only                                                                                                                       |

| Anritsu 41KC-3                     | 2    | Attenuator                                                                                                                                                    | Applies for MP1800A BERT only                                                                                                                       |

| Anritsu 41KC-6                     | 2    | Attenuator                                                                                                                                                    | Applies for MP1800A BERT only                                                                                                                       |

| Anritsu 41KC-20                    | 2    | Attenuator                                                                                                                                                    | Applies for MP1800A BERT only                                                                                                                       |

| Anritsu J1510A                     | 2    | Pick-off Tees                                                                                                                                                 | Applies for MP1800A BERT only                                                                                                                       |

| Anritsu 34VKF50A                   | 2    | V(m) - K(f) Coaxial Adapter                                                                                                                                   | *Only required if using a PAM4 Pulse<br>Pattern Generator                                                                                           |

| Equipment | Qty. | Description                     | Key Specification Requirement |

|-----------|------|---------------------------------|-------------------------------|

| Computer  | 1    | Laptop or desktop (Windows 7+ C | S) for automation control     |

<sup>&</sup>lt;sup>[a]</sup> Oscilloscope with scope software requirements as specified in vendor specific MOI's. For example, when using the Keysight Scope, scope software such as Keysight InfiniiSim / EZ-JIT / Serial Data Analysis / Serial Data Equalization that are required for testing and signal processing must be pre-installed on the Scope. Similarly, the Tektronix Scope shall be used with DPOJET (Jitter and Eye Analysis Tools) software for making measurements.

**Note:** Cable connector type and length requirements may vary according to the lab setup and the dimensions of the DUT board. Table below is a recommended list. Please also refer to the respective manufacturer for detailed cabling recommendations related to PCI Express.

TABLE 2. EQUIPMENT REQUIREMENTS – CABLES

| Cable                                                                                        | Qty.    | Key Specification Requirement                                                                                                                                            |

|----------------------------------------------------------------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Anritsu J1508A BNC to SMA cable pair                                                         | 1 pair  | For MU181000A/B to MU181500B                                                                                                                                             |

| Anritsu J1349A SMA-SMA cable                                                                 | 2       | 30cm                                                                                                                                                                     |

| Anritsu J1343A SMA-SMA cable                                                                 | 4       | 100cm                                                                                                                                                                    |

| Anritsu J1551A or Huber Suhner 0130-314-00<br>SMA-SMA phase matched cable pair               | 2 pairs | 3ft                                                                                                                                                                      |

| Anritsu J1615A K-K cable set                                                                 | 1       | For MU183020A PPG clock (130cm) / data (80cm) to connect to MP1825B deemphasis box (if using MP1800A BERT)  Or  For MU195050A output connections (if using MP1900A BERT) |

| Rosenberger L71-456-102 or Rosenberger<br>RNA 0111 603841, phase matched SMA-SMP<br>adapters | 2 pairs |                                                                                                                                                                          |

<sup>[</sup>b] Oscilloscope with scope bandwidth as specified in vendor specific MOI's.

<sup>[</sup>c] The GRL-PCIE4-BASE-RXA software supports the NRZ or PAM4 signal.

<sup>[</sup>d] The Artek CLE Model Series is supported for variable ISI generation. Refer to Appendix of this document for the Artek CLE Series driver installation procedure.

# 2.2 Software Requirements

TABLE 3. SOFTWARE REQUIREMENTS

| Software                                                           | Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GRL-PCIE4-BASE-RXA <sup>[a]</sup>                                  | Granite River Labs PCIe® 4.0 (16 GT/s and 8 GT/s) Base Specification Receiver Calibration and Test Automation Software – <a href="www.graniteriverlabs.com">www.graniteriverlabs.com</a> Included with Node Locked License to single oscilloscope or PC OS                                                                                                                                                                                                                                                                                              |

| VISA (Virtual Instrument<br>Software Architecture) API<br>Software | VISA Software is required to be installed on the controller PC running GRL-PCIE4-CEM-RXA software. GRL's software framework has been tested to work with all three versions of VISA available on the Market:  1. NI-VISA: <a href="http://www.ni.com/download/ni-visa-17.0/6646/en/">http://www.ni.com/download/ni-visa-17.0/6646/en/</a> 2. Keysight IO Libraries: <a href="http://www.keysight.com">www.keysight.com</a> (Search on IO Libraries) 3. Tektronix TekVISA: <a href="http://www.tek.com">www.tek.com</a> (Downloads > Software > TekVisa) |

| Seasim                                                             | Seasim tool for post-process analysis of the captured waveform (Eye Opening simulation software at TP2P) – <a href="https://www.pcisig.com">www.pcisig.com</a> Used for Channel (DDJ) calibration                                                                                                                                                                                                                                                                                                                                                       |

| SigTest                                                            | Standard Post Processing Analysis Software – www.intel.com/content/www/us/en/design/technology/high-speed- io/tools.html SigTest used with Seasim for final eye calibration                                                                                                                                                                                                                                                                                                                                                                             |

| MX183000A                                                          | Anritsu High-Speed Serial Data Test Software – For loopback BER testing of the PCIe Gen 4 Base Rx DUT. This software is located on the BERT.                                                                                                                                                                                                                                                                                                                                                                                                            |

<sup>[</sup>a] PCIe3-BASE and PCIe4-BASE will need to be installed to test at both 16 GT/s and 8 GT/s data rates. If the GRL-PCIE4-RXA test solution is purchased, the user will need to install the GRL-PCIE4-BASE-RXA and GRL-PCIE4-CEM-RXA solutions included in the package to perform testing for PCIe4-BASE and PCIe4-CEM at 16 GT/s and 8 GT/s.

# 3 Setting Up GRL-PCIE4-BASE-RXA Software

This section provides procedures for installing, configuring and verifying the operation of the GRL-PCIE4-BASE-RXA PCIe 4.0 Base Receiver Test software at 16 GT/s. It also helps you familiarize yourself with the basic operation of the application.

The software installer automatically creates shortcuts in the Desktop and Start Menu.

To open the application, follow the procedure in the following section.

#### 3.1 Download GRL-PCIE4-BASE-RXA Software

Install, launch and set up the GRL-PCIE4-BASE-RXA software:

- 1. If the GRL-PCIE4-BASE-RXA software is to be installed on a PC (where it is referred to as 'controller PC'), install VISA (Virtual Instrument Software Architecture) on to the PC where the GRL software is to be used (see Section 2.2).

- 2. Download the software ZIP file package from the Granite River Labs support site.

- 3. The zip file contains:

- **PCIe4\_0\_BaseANPatternFilesInstallation001xxxxxxxSetup.exe** Run this on the Anritsu Signal Quality Analyzer to install the test pattern setup files.

- **PCIEGen4ANBaseSpecTestApplication001xxxxxxxxSetup.exe** Run this on the controller PC or oscilloscope to install the GRL-PCIE4-BASE-RXA application.

- PCIe4\_0\_BaseANRxTestScopeSetupFilesInstallation001xxxxxxxSetup.exe Run this

on the oscilloscope to install the scope setup files.

## 3.2 Launch and Set Up GRL-PCIE4-BASE-RXA Software

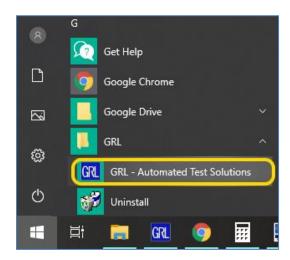

Once the software is installed, open the GRL folder from the Windows Start menu. Click on GRL – Automated Test Solutions within the GRL folder to launch the GRL software framework.

#### FIGURE 1. SELECT AND LAUNCH GRL FRAMEWORK

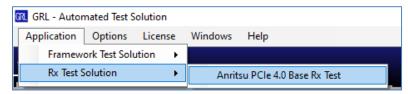

2. From Application → Rx Test Solution drop-down menu, select "Anritsu PCIe 4.0 Base Rx Test". If the selection is grayed out, it means that your license has expired.

FIGURE 2. START PCIE 4.0 BASE RX TEST APPLICATION

3. To enable license, go to License → License Details.

FIGURE 3. SEE LICENSE DETAILS

a) Check the license status for the installed application.

FIGURE 4. CHECK LICENSE FOR INSTALLED APPLICATIONS

- b) Activate a License:

- If you have an Activation Key, enter it in the field provided and select "Activate".

• If you do not have an Activation Key, select "Close" to use a demo version of the software over a free 10-day trial period.

**Note:** Once the 10-day trial period ends, you will need to request an Activation Key to continue using the software on the same computer or oscilloscope. The demo software is also limited in its capability, in that it will only calibrate the maximum frequency for each data rate. Thus, the demo version cannot be used to fully calibrate and test a device. For Demo and Beta Customer License Keys, please request an Activation Key by contacting <a href="mailto:support@graniteriverlabs.com">support@graniteriverlabs.com</a>.

#### 3.2.1 Connection Configuration on the Scope or Controller PC OS

### 3.2.1.1 Connecting Anritsu Signal Quality Analyzer BERT with Scope or PC

Connect the Anritsu BERT via LAN to the GRL automation control enabled Scope or PC. The BERT and MX183000A software can be connected using connection string formats similar to the following examples:

- BERT: "TCPIP0::192.168.0.14::5001::SOCKET" or "192.168.0.14:5001"

- MX183000A: "TCPIP0::192.168.0.14::5000::SOCKET" or "192.168.0.14:5000"

Note the IP addresses listed above are only examples and should be changed according to the actual network connection being used.

#### 3.2.1.2 Connecting Anritsu MG3710A with Scope or PC

Connect the Anritsu Vector Signal Generator via LAN to the GRL automation control enabled Scope or PC.

#### 3.2.1.3 Connecting Artek CLE Series with Scope or PC

Connect the Artek ISI Generator via USB to the GRL automation control enabled Scope or PC. (Note: The USB driver software for the ISI Generator must be installed on the PC. The driver is available from the ISI Generator manufacturer. Refer to Appendix of this MOI for driver installation information.)

### 3.2.1.4 Connecting Oscilloscope with PC

Connect the oscilloscope with the GRL automation control enabled PC through either GPIB, USB or LAN. (Note: Additional information for connecting the Keysight and Tektronix oscilloscopes to the controller PC is provided in the Appendix of this MOI.)

#### 3.2.1.5 On the Scope or PC

- 1. Launch GRL Host Application from Start Menu -> GRL -> GRL Automated Test Solutions.

- 2. Select Application -> Rx Test Solution -> Anritsu PCIe 4.0 Base Rx Test Application.

- 3. On the Scope or PC, obtain the network addresses for all the connected instruments from the device settings. Note these addresses as they will be used to connect the instruments to the GRL automation software.

- 4. On the Equipment Setup page of the GRL PCIe 4.0 Base Rx Test Application, type in the address of each connected instrument into the 'Address' field.

(Note: If the GRL software is installed on the **Tektronix Scope**, ensure the Scope is connected via GPIB and type in the GPIB network address, for example "GPIB8::1::INSTR".)

If the GRL software is installed on the PC to control the Scope, type in the Scope IP address, for example "TCPIP0::192.168.0.110::inst0::INSTR". Note to **omit** the Port number from the address.

(Note: If the GRL software is installed on the **Keysight Scope**, and if there is error in connection, type in the Scope IP address as "TCPIPO::192.168.0.4::5025::SOCKET".)

Then select the "lightning" button ( ) for each connected instrument.

The "lightning" button should turn green ( once the software has successfully established connection with each instrument.

FIGURE 5. CONNECT INSTRUMENTS WITH GRL SOFTWARE

(Note: Additional information for connecting the Keysight and Tektronix oscilloscopes to the PC is provided in the Appendix of this User Guide & MOI.)

## 3.3 Configure the GRL-PCIE4-BASE-RXA Software Before Calibration

Once all equipment is successfully connected from the previous section, proceed to set up the preliminary settings before going to the advanced measurement setup.

#### 3.3.1 Enter Test Session Information

Select from the menu to access the **Session Info** page. Enter the information as required for the test session that is currently being run. The information provided will be included in the test report generated by the software once tests are completed.

- The fields under **DUT Info** and **Test Info** are defined by the user.

- The **Software Info** field is automatically populated by the software.

FIGURE 6. SESSION INFO PAGE

### 3.3.2 Set Measurement Conditions

Select from the menu to access the **Conditions** page to set the conditions for calibration and testing.

Recommended procedure:

- *Step 1*: When calibrating, select all required conditions and perform the calibration.

- Step 2: Once calibration is completed and ready for testing, re-select the conditions that will be used for specific tests.

SJ tab: Select SJ Frequencies as defined by the Specification for calibration or testing.

FIGURE 7. SELECT SJ FREQUENCIES

### 3.3.3 Setup Configuration

Select from the menu to access the **Setup Configuration** page to configure the calibration/test parameters.

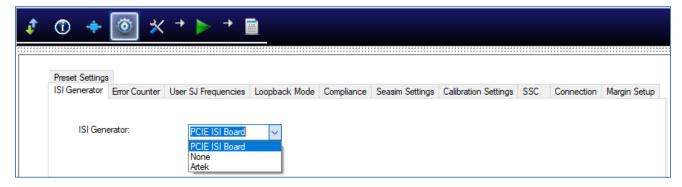

#### 3.3.3.1 ISI Generator Setup

Select the type of supported ISI generators to be used:

- "None": This is the recommended method which is used to provide 22 to 27 dB physical channel Insertion Loss for calibration and testing. A PCIe 4.0 CEM Fixture can be used in the setup for this method.

- "Artek": This is provided as an Option. The Artek CLE1000-S2 ISI channel and an additional ISI board can be used in the setup for ISI automation. (Also see Appendix for more information on installing the Artek CLE Series.)

- "PCIe ISI Board": This is provided as an Option which can be used to measure Insertion Loss when a Vector Network Analyzer is not available.

FIGURE 8. ISI GENERATOR SETUP

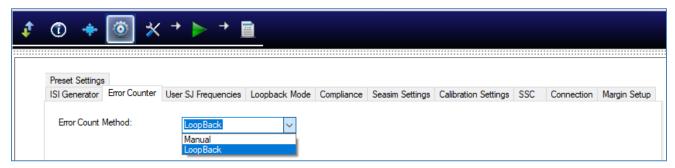

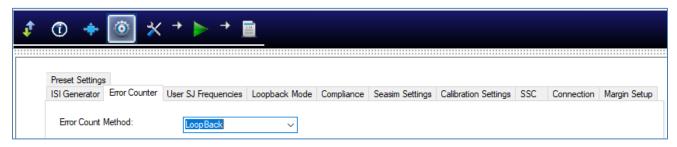

#### 3.3.3.2 Error Counter Setup

Enable loopback test mode for the Rx base DUT for error detection. If the DUT can be configured to loopback mode, select 'LoopBack', if not select 'Manual'.

FIGURE 9. BER LOOPBACK TEST METHOD

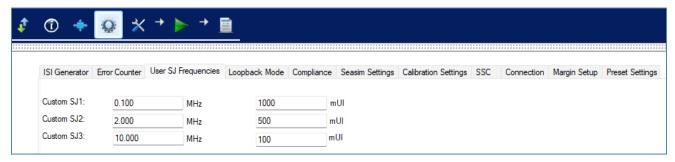

#### 3.3.3.3 User SJ Frequencies Setting

Set custom SJ frequencies to test for condition setup on the Conditions page.

FIGURE 10. USER SJ FREQUENCIES SETTING

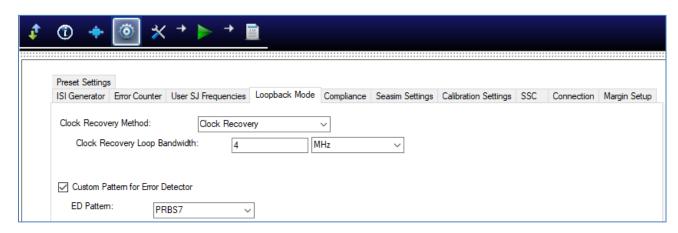

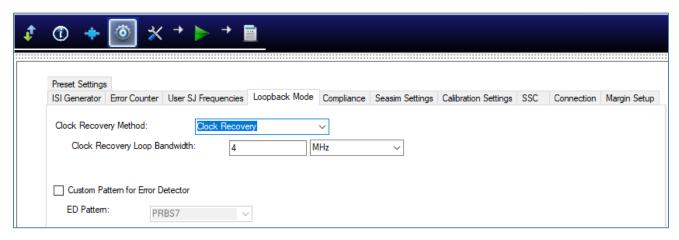

### 3.3.3.4 Loopback Mode Setup

If "LoopBack" has been selected from the Error Counter tab, then select "Clock Recovery" in the Clock Recovery Method drop-down on the Loopback Mode tab. *Other options on the Clock Recovery Method drop-down are not yet supported.*

If a Custom Pattern is to be used for error detection analysis, select the checkbox and then select the test pattern type. If the checkbox is not selected, a default test pattern will be used.

FIGURE 11. LOOPBACK MODE SETUP

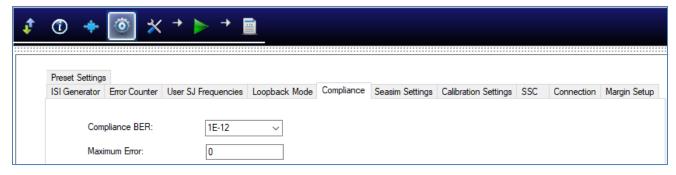

#### 3.3.3.5 Compliance BER Setup

Set the allowable BER and Maximum Error limits to be tested for compliance. By default, these limits are set to Specification, but can be defined by the user. The syntax '1e-12' indicates 1x10<sup>-12</sup>, and is the only syntax supported in this field. In normal circumstances, any error count above one constitutes a fail.

FIGURE 12. COMPLIANCE BER AND MAXIMUM ERRORS SETUP

#### 3.3.3.6 Seasim Settings

Set up user-defined Rx Behavioral package to be applied during post processing analysis for the Eye Height and Eye Width Calibration. Also set the intrinsic jitter (if required) to be used in the Seasim calculation.

FIGURE 13. SEASIM SETTINGS

#### 3.3.3.7 DM and CM Calibration Settings

Specify or use the default frequency values for Differential Mode (DM) and Common Mode (CM) calibration.

FIGURE 14. DM AND CM CALIBRATION SETTINGS

#### 3.3.3.8 Spread Spectrum Clock (SSC) Setup

Select the checkbox to enable SSC capabilities for calibration and receiver testing (if supported by the DUT) for informative purpose. Set the Frequency and Deviation values for SSC.

FIGURE 15. SSC SETUP

#### 3.3.3.9 Connection Setup

Set to use Real Edge connection for test setup on the Oscilloscope. *Note: This setting is only applicable for the Keysight Scope and will be disabled when the Tektronix Scope is used.*

FIGURE 16. CONNECTION SETUP

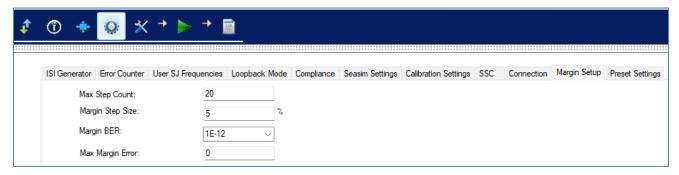

### 3.3.3.10 Margin Setup

Select the target BER, step size, and limits to be applied during marginal testing.

FIGURE 17. MARGIN SEARCH PARAMETERS SETUP

### 3.3.3.11 Preset Settings

Select the preset to be used, and optionally custom Pre-shoot and De-emphasis settings.

FIGURE 18. PRESET SETTINGS

# 4 Calibrating Using GRL-PCIE4-BASE-RXA Software

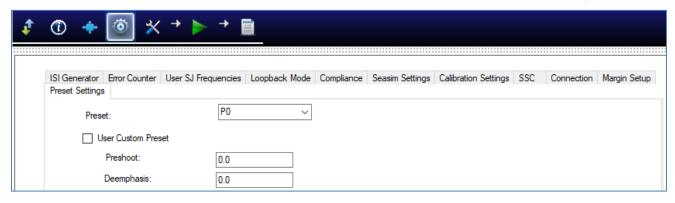

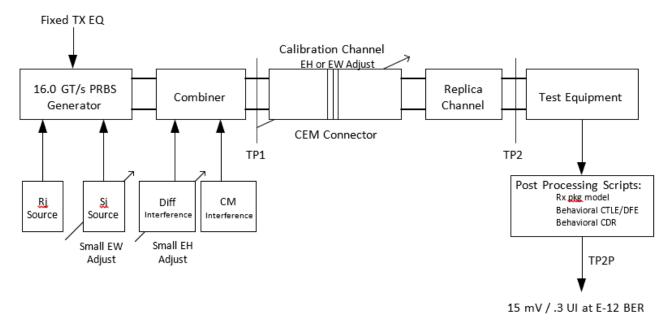

Calibration for PCI Express 4.0 Base Specification are performed at two physical test points – TP1 and TP2. TP1 is a physical test point for calibration without the effect of a channel. An adjustable Calibrated CEM connector is defined that is to be used along with the Replica Channel for the DUT for testing. TP2 is a physical test point that will affect the eye opening due to trace length. Post processing analysis of the signal is performed at the TP2P test point using the Seasim or SigTest application to simulate the stressed eye opening after applying Rx Behavioral package, Rx CTLE, and DFE (if required).

FIGURE 19. RX CALIBRATION BLOCK DIAGRAM FROM THE PCIE 4.0 BASE SPECIFICATION

To calibrate the stressed eye at TP2, the calibration channel shall receive signals with appropriate test patterns generated by the signal source. After calibration, the signal source shall be used for testing Rx DUT compliance.

FIGURE 20. RX CALIBRATION/TEST SCHEMATIC OVERVIEW FROM THE PCIE 4.0 BASE SPECIFICATION

# 4.1 Calibration for TP1 (Output of BERT Generator)

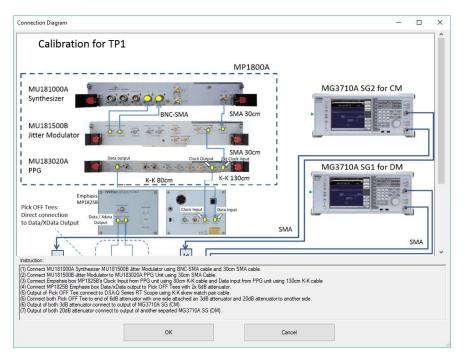

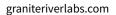

### 4.1.1 Setup for TP1 Calibration (Using MP1800A BERT)

FIGURE 21. TYPICAL SETUP FOR TP1 CALIBRATION (USING MP1800A BERT)

### **Connection Steps:**

- 1. Using the BNC-SMA Cable Pair (Anritsu J1508A), connect the MU181000A Synthesizer Ext I\_Ext Q to the MU181500B Jitter Modulator I\_Q output.

- 2. Using the 30cm SMA-SMA short cable (Anritsu J1349A), connect the MU181000A Synthesizer clock output to the MU181500B Jitter Modulator Ext clock input.

- 3. Using the 30cm SMA-SMA short cable (Anritsu J1349A), connect the MU181500B Jitter Modulator jittered clock output to the MU183020A PPG Ext clock input.

- 4. Using the 80cm K-K cable (Anritsu J1615A), connect the MU183020A PPG data output to the MP1825B De-emphasis Box data input.

- 5. Using the 130cm K-K cable (Anritsu J1615A), connect the MU183020A PPG clock output to the MP1825B De-emphasis Box clock input.

- 6. Assign the MP1825B as a Slot number on the MP1800A GUI.

- 7. Connect the MP1825B data/Xdata output to the Pick-off Tees (Anritsu J1510A) with two 6dB attenuators (Anritsu 41KC-6).

- 8. Using a K-K skew matched cable pair, connect the outputs of the Pick-off Tees to the DSA-Q Series RT Scope.

- 9. Connect both Pick-off Tees to the ends of the 6dB attenuators with a 3dB attenuator (Anritsu 41KC-3) attached on one side and a 20dB (Anritsu 41KC-20) attenuator on another side.

- 10. Using the 100cm SMA-SMA long cables (Anritsu J1343A), connect both 3dB attenuators to the outputs of the MG3710A SG (for CM).

- 11. Using the 100cm SMA-SMA long cables (Anritsu J1343A), connect both 20dB attenuators to the outputs of another MG3710A SG (for DM).

#### 4.1.2 Setup for TP1 Calibration (Using MP1900A BERT)

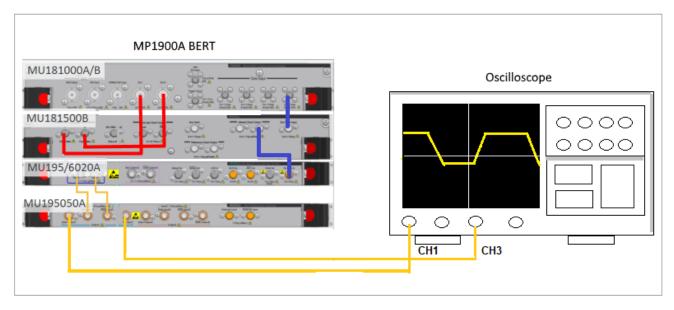

FIGURE 22. TYPICAL SETUP FOR TP1 CALIBRATION (USING MP1900A BERT)

**Connection Steps:**

- 1. Using a SMA-SMA short cable, connect the MU181000A/B clock output to the MU181500B Ext clock input.

- 2. Using a SMA-SMA short cable, connect the MU181500B jittered clock output to the MU195020A/MU196020A Ext clock input.

- 3. Using BNC-SMA cables, connect the MU181000A/B Ext I\_Ext Q to the MU181500B I\_Q output.

- 4. Using coaxial cables, connect the MU195020A/MU196020A data outputs to the MU195050A data inputs.

- 5. Using phase matched K-K coaxial cables, connect the MU195050A data outputs to Channels 1 and 3 on the oscilloscope.

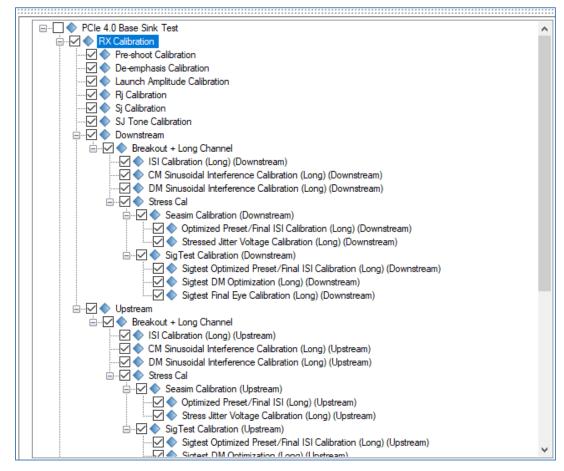

#### 4.1.3 Select Calibration

The following calibration are defined at TP1 and TP2 Test Points.

#### Calibration at TP1:

- 1. PG Delay Calibration (Only applicable if using the MP1800A BERT)

- 2. Pre-shoot Calibration

- 3. De-emphasis Calibration

- 4. Launch Amplitude Calibration

- 5. RJ Calibration

- 6. SJ Calibration

- 7. SJ Tone Calibration

#### Calibration at TP2, can be Downstream (for Host) or Upstream (for Device):

- 8. Downstream or Upstream:

- a. Insertion Loss Calibration [Only applicable if CTS version '0.7' is selected from the Configurations page menu see Section 4.1.4]

- b. ISI Calibration (CEM Connector Channel + Replica Channel) [Only applicable if CTS version '1.0' is selected from the Configurations page menu see Section 4.1.4 AND ISI Generator other than "None" is selected from the Setup Configuration menu see Section 3.3.3.1]

- c. Common Mode (CM) Sinusoidal Interference Calibration

- d. Differential Mode (DM) Sinusoidal Interference Calibration (Achieves Calibrated Eye Height)

- e. Final ISI Calibration

- f. Stressed Jitter Voltage Calibration (Final stressed voltage and jitter eye adjustment to achieve Calibrated Eye Width)

- g. SigTest DM Optimization & Final Eye Calibration (Produces final stressed Eye Diagram if SigTest is used as post processing tool)

- [SigTest Final Eye Calibration is only applicable if CTS version '1.0' is selected from the Configurations page menu see Section 4.1.4]

GRL-PCIE4-BASE-RXA automatically calibrates these parameters when initiated. See Appendix for an implementation method with automation for the above calibration.

The test selection list allows calibration/tests that need to be performed to be selected. Initially, when starting for the first time or changing anything in the setup, it is suggested to run Calibration first. If the calibration is not completed, the Rx Tests will throw an error when initiated.

FIGURE 23. CALIBRATION SELECTION

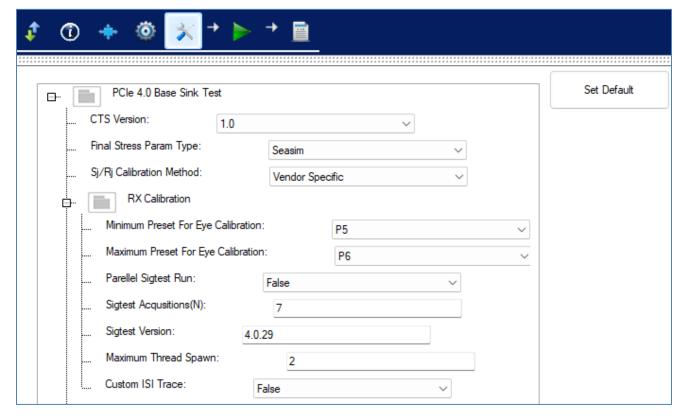

### 4.1.4 Configure Calibration Parameters

After selecting the desired calibration, select from the menu to access the **Configurations** page. Set the required parameters for calibration as described below.

To return all parameters to their default values, select the 'Set Default' button.

FIGURE 24. CALIBRATION PARAMETERS CONFIGURATION PAGE

TABLE 4. CALIBRATION PARAMETERS DESCRIPTION

| Parameter                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CTS Version                    | Select the Version of the CTS that is used as the reference specs to perform calibration and tests. (Note: This selection causes the Select Tests page to display different test lists for the specific CTS version.)                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| Final Stress Parameter<br>Type | Select either the SigTest or Seasim application to be used for post processing signal quality testing. Make sure that the SigTest or Seasim application is already installed in the test controller system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| SJ/RJ Calibration<br>Method    | <ul> <li>Select the SigTest, a vendor-specific, or a system-defined based methodology to be applied during calibration of SJ or RJ:</li> <li>Select the 'SigTest' option to apply the SigTest method for calibration of all SJ/RJ frequencies; or</li> <li>Select the 'Vendor Specific' option to use the Vendor-specific method (Tektronix DPOJET or Keysight EZ-JIT Plus software) for calibration of all SJ/RJ frequencies; or</li> <li>Select the 'System Defined' option to use the Vendor-specific method (Tektronix DPOJET or Keysight EZ-JIT Plus software) for low SJ frequency calibration and the SigTest method for high SJ frequency and RJ calibration.</li> </ul> |  |

| Minimum & Maximum Preset for Eye Calibration | Select the range of presets to be applied for stressed eye calibration.                                                   |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Parallel SigTest Run                         | Select 'True' to enable running the SigTest application in parallel mode with the Long Channel TP2 calibration.           |

| SigTest Acquisitions (N)                     | Enter the number of measurements to acquire when running the SigTest application over the Long Channel TP2 calibration.   |

| SigTest Version                              | Enter the Version number of the SigTest application if used.                                                              |

| Maximum Thread<br>Spawn                      | Set the maximum process threads to generate for checking the Rx device functionality during Long Channel TP2 calibration. |

| Custom ISI Trace                             | Select 'True' to enable generating custom ISI trace for ISI calibration.                                                  |

#### 4.1.5 Run Calibration at TP1

Select the Run icon:

**Skip Test if Result Exists.** If previous calibration results exist, then the software will *skip* the calibration steps that have existing reports.

**Replace if Result Exists.** If previous calibration results exist, then the software will *replace* each step in the calibration with new results.

FIGURE 25. RUN TESTS

When running Calibration at TP1, the connection diagram will be shown as a first step to help the user make sure all connections are made before the tests are run. See Figure 26.

FIGURE 26. TP1 CONNECTION DIAGRAM DIALOG

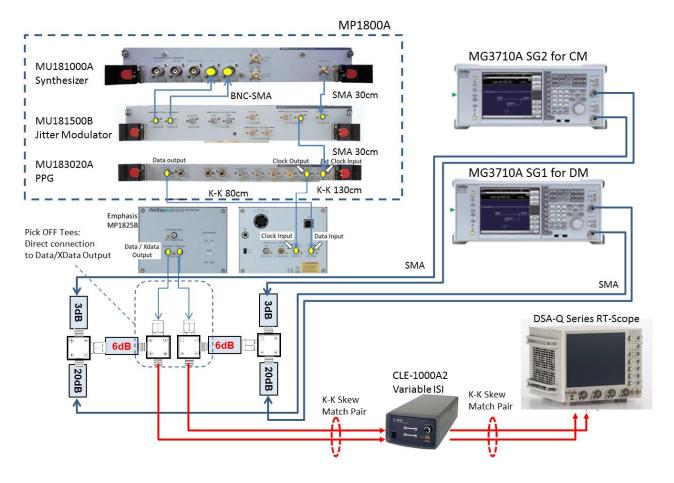

### 4.2 Calibration for TP2 (Output of Long Channel)

The next step is to calibrate the TP1-TP2 Channel. As shown in Figure 19, the total TP1-TP2 calibration channel includes an Adjustable Calibration Channel, that requires the Insertion loss to fit within the limits called out in the PCI Express 4.0 Base specification.

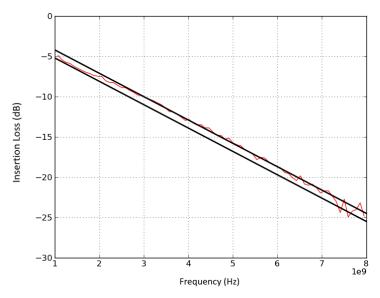

The GRL-PCIE4-BASE-RXA software uses a combination of a variable ISI channel, CEM connector, and replica channel to achieve the target IL profile. After calibrated using the GRL software, the calibrated channel IL should look like the example shown in Figure 28 after being analyzed with a post processing tool.

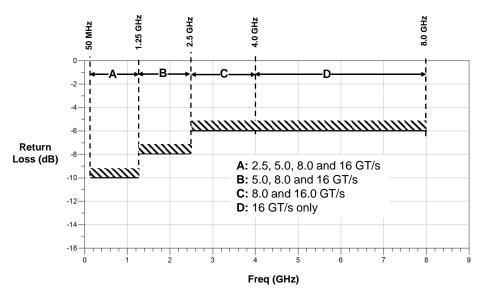

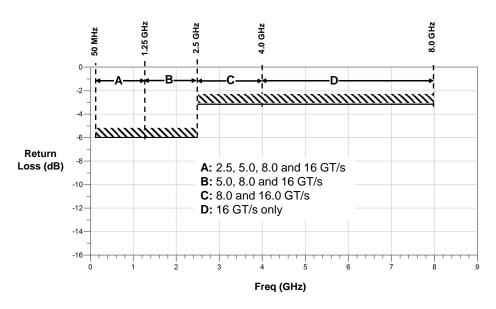

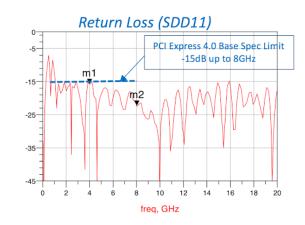

Note: The PCIe 4.0 Base Specification requires the calibration channel to meet a return loss (RL) mask at -15 dB up to Nyquist. See Appendix for more details on the return loss specs.

#### 4.2.1 Setup for TP2 Calibration (Using MP1800A BERT)

FIGURE 27. TYPICAL SETUP FOR TP2 CALIBRATION (USING MP1800A BERT)

#### **Connection Steps:**

- 1. Using the BNC-SMA Cable Pair (Anritsu J1508A), connect the MU181000A Synthesizer Ext I\_Ext Q to the MU181500B Jitter Modulator I\_Q output.

- 2. Using the 30cm SMA-SMA short cable (Anritsu J1349A), connect the MU181000A Synthesizer clock output to the MU181500B Jitter Modulator Ext clock input.

- 3. Using the 30cm SMA-SMA short cable (Anritsu J1349A), connect the MU181500B Jitter Modulator jittered clock output to the MU183020A PPG Ext clock input.

- 4. Using the 80cm K-K cable (Anritsu J1615A), connect the MU183020A PPG data output to the MP1825B De-emphasis Box data input.

- 5. Using the 130cm K-K cable (Anritsu J1615A), connect the MU183020A PPG clock output to the MP1825B De-emphasis Box clock input.

- 6. Assign the MP1825B as a Slot number on the MP1800A GUI.

- 7. Connect the MP1825B data/Xdata output to the Pick-off Tees (Anritsu J1510A) with two 6dB attenuators (Anritsu 41KC-6).

- 8. Using a K-K skew matched cable pair, connect the outputs of the Pick-off Tees to the Artek Variable ISI Generator.

- 9. Using a K-K skew matched cable pair, connect the Artek outputs to the DSA-Q Series RT Scope.

- 10. Connect both Pick-off Tees to the ends of the 6dB attenuators with a 3dB attenuator (Anritsu 41KC-3) attached on one side and a 20dB (Anritsu 41KC-20) attenuator on another side.

- 11. Using the 100cm SMA-SMA long cables (Anritsu J1343A), connect both 3dB attenuators to the outputs of the MG3710A SG (for CM).

- 12. Using the 100cm SMA-SMA long cables (Anritsu J1343A), connect both 20dB attenuators to the outputs of another MG3710A SG (for DM).

FIGURE 28. CALIBRATED IL EXAMPLE USING GRL-PCIE4-BASE-RXA

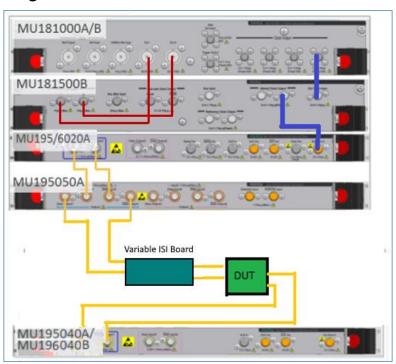

#### 4.2.2 Setup for TP2 Calibration (Using MP1900A BERT)

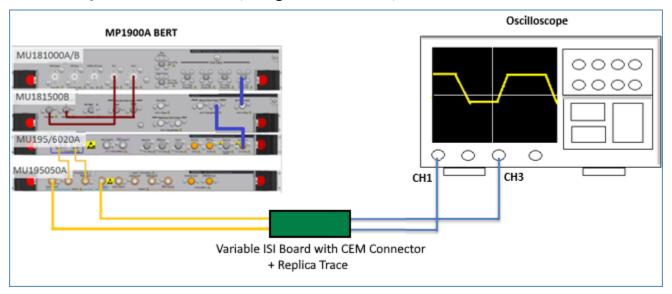

FIGURE 29. TYPICAL SETUP FOR TP2 CALIBRATION (USING MP1900A BERT)

#### **Connection Steps:**

- 1. Using back the same BERT connections from the TP1 calibration, disconnect the MU195050A data outputs from the oscilloscope channels.

- 2. Connect the MU195050A data outputs to the variable ISI board (with CEM connector and replica trace).

- 3. Connect the variable ISI board to Channels 1 and 3 on the oscilloscope.

#### 4.2.3 Run Calibration Steps at TP2

Repeat Section 4.1.3 to complete the selected calibration steps at TP2.

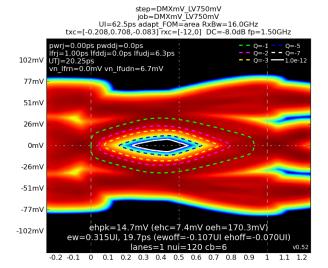

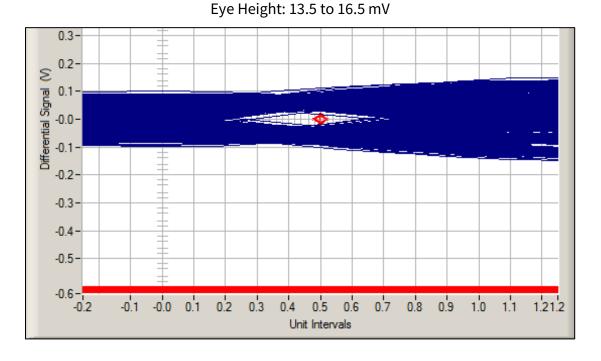

After Calibrating the Loss profile to be used by adjustment of De-Emphasis, ISI Measurement, CM Sinusoidal Interference, DM Sinusoidal Interference, Final ISI and SJ adjustments to achieve calibrated eye height and width, the final calibrated stressed Eye diagram is calculated by Seasim and SigTest, and should look similar to the below example.

FIGURE 30. FINAL CALIBRATED STRESSED EYE DIAGRAM EXAMPLE

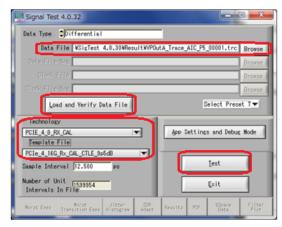

### 4.2.4 Set Up SigTest for Final Stressed Eye Calibration

The following example describes how to use the SigTest post processing tool to achieve the final calibrated stressed Eye diagram.

Assuming waveforms have been captured on the Scope for each test condition, set up the following parameters to analyze Eye Height/Eye Width using SigTest.

Note below settings are example of a typical setup for final eye calibration.

- a) BERT Settings:

- General Output: ON

- Select SI-PPG and Emphasis tab- Emphasis Function: ON

- Select the Pattern tab- Test Pattern: 128b130b\_CP\_L0\_Gen4\_P0

- Set all Jitter, Noise, and Amplitude values.

- Save five waveforms and read in SigTest.

- Adjust Eye Height/Eye Width to target specification values using SJ, DM-I, Eye Amplitude.

- b) Scope Settings:

- Averaging: OFF

- Set appropriate Horizontal Scale and Bandwidth

- c) SigTest Settings:

- Select a Data File

- Select 'Load and Verify Data File'

- Select Technology as 'PCIE\_4\_0\_RX\_CAL'

- Select Template File as 'PCIe\_4\_16G\_Rx\_CAL\_CTLE\_x.xdB'

- Select 'Test'

(Note: Use the current version of SigTest, V4.0.38 with the PCIe\_4\_16G\_Rx\_CAL\_CTLE\_x.xdB.dat template file- 8 dB to 9.5 dB in ¼ dB steps CTLE curves allowed for each Tx preset.)

### d) SigTest Results:

Note that the SigTest Full Test Result always shows 'Fail!' which can be ignored.

Min Eye Width: 18.25 to 19.25 ps

#### Notes:

- Locate the largest loss channel (27 dB to 30 dB) where the Eye Width/Eye Height is above the calibration target value.

- o Save more than five waveforms and obtain the average value.

For final eye calibration, adjust Voltage Swing, SJ, and DM Amplitude until the target Eye Width and Eye Height are achieved.

## 5 Testing Using GRL-PCIE4-BASE-RXA Software

Once the final stressed eye has been calibrated successfully, receiver stress jitter voltage tolerance and margin testing can then be performed on the device under test (DUT). The DUT should have a Replica Channel of the same Insertion Loss as the Replica Channel used for calibration. The Replica Channel is removed when performing the DUT tests.

The GRL-PCIE4-BASE-RXA software automates the receiver compliance and jitter tolerance testing, at the spec-defined or user-defined jitter frequency steps. The GRL software also supports nested loop testing of multiple parameters to facilitate silicon PVT testing or testing across multiple test conditions. When testing is completed, the results will be logged in an aggregated test report which can be generated into a PDF format.

Receiver device compliance ensures the receiver DUT is able to correctly interpret data from a received signal with valid voltage and timing characteristics by achieving an acceptable bit error ratio (BER) of less than 1E-12. The signal used for verifying receiver tolerance must contain the maximum allowable jitter, noise, and signal loss. The stressed receiver tolerance test should include various differential mode sinusoidal interference, minimum transmitter voltage amplitude, and jitter which includes random jitter and a sinusoidal periodic jitter component that is swept across specific frequency intervals.

Once the stressed receiver tolerance test setup has been calibrated, the BERT will transmit a modified compliance pattern to the receiver and monitors the loopback pattern has a BER that is less than 1E-12.

#### 5.1 Receiver DUT Compliance Test Setup

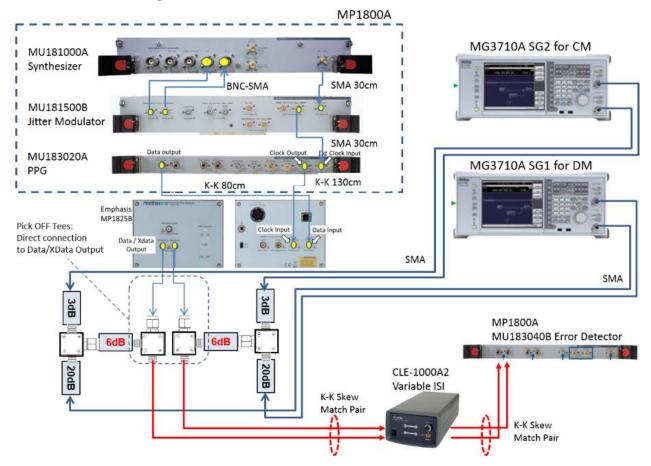

#### 5.1.1 Test Setup Using MP1800A BERT

FIGURE 31. TYPICAL RECEIVER DUT TEST SETUP (USING MP1800A BERT)

Note: The Artek CLE Series Variable ISI Generator is used to replace the Calibration Channel + Breakout Channel.

#### **Connection Steps:**

- 1. Using the BNC-SMA Cable Pair (Anritsu J1508A), connect the MU181000A Synthesizer Ext I\_Ext Q to the MU181500B Jitter Modulator I\_Q output.

- 2. Using the 30cm SMA-SMA short cable (Anritsu J1349A), connect the MU181000A Synthesizer clock output to the MU181500B Jitter Modulator Ext clock input.

- 3. Using the 30cm SMA-SMA short cable (Anritsu J1349A), connect the MU181500B Jitter Modulator jittered clock output to the MU183020A PPG Ext clock input.

- 4. Using the 80cm K-K cable (Anritsu J1615A), connect the MU183020A PPG data output to the MP1825B De-emphasis Box data input.

- 5. Using the 130cm K-K cable (Anritsu J1615A), connect the MU183020A PPG clock output to the MP1825B De-emphasis Box clock input.

- 6. Connect the MP1825B data/Xdata output to the Pick-off Tees (Anritsu J1510A) with two 6dB attenuators (Anritsu 41KC-6).

- 7. Using a K-K skew matched cable pair, connect the outputs of the Pick-off Tees to the Artek Variable ISI Generator.

- 8. Connect the Artek outputs to the DUT's input.

- 9. Using a K-K skew matched cable pair, connect the DUT's Tx Out to the MU183040B Error Detector data input.

- 10. Connect both Pick-off Tees to the ends of the 6dB attenuators with a 3dB attenuator (Anritsu 41KC-3) attached on one side and a 20dB (Anritsu 41KC-20) attenuator on another side.

- 11. Using the 100cm SMA-SMA long cables (Anritsu J1343A), connect both 3dB attenuators to the outputs of the MG3710A SG (for CM).

- 12. Using the 100cm SMA-SMA long cables (Anritsu J1343A), connect both 20dB attenuators to the outputs of another MG3710A SG (for DM).

#### 5.1.2 Test Setup Using MP1900A BERT

FIGURE 32. TYPICAL RECEIVER DUT TEST SETUP (USING MP1900A BERT)

Note: The Variable ISI Board is used to replace the Calibration Channel + Breakout Channel.

#### **Connection Steps:**

- 1. Using back the same BERT connections from calibration, connect the MU195050A data outputs to the variable ISI board.

- 2. Using coaxial cables, connect the variable ISI board to the DUT Rx inputs.

- 3. Using phase matched K-K coaxial cables, connect the DUT Tx outputs to the MU195040A (or MU196040B if using a PAM4 Error Detector) data inputs for loopback error detection.

#### 5.1.3 Receiver Compliance Tests

In the following diagram, **Select Tests > Stress Jitter Voltage** tests are selected if tests at the Compliance Jitter Limits are to be performed.

FIGURE 33. SELECTING RECEIVER COMPLIANCE TESTS

The stress jitter voltage tests are run from the same screen as shown in Figure 25.

#### 5.1.4 Receiver Margin Tests

In the following diagram, **Select Tests > Stress Jitter Voltage Margin** tests are selected if Jitter Margin testing is to be performed.

FIGURE 34. SELECTING RECEIVER MARGIN TESTS

The marginal tests are run from the same screen as shown in Figure 25.

#### 5.1.5 Apply Calibrated Values for Testing

Calibrated values from the stressed jitter voltage calibration can be used in the DUT Rx tests. To apply these values, go to **Select Tests > Apply Stress Voltage Param**.

FIGURE 35. SELECTING TO APPLY CALIBRATION VALUES

#### 5.1.6 Configure Receiver Test Parameters

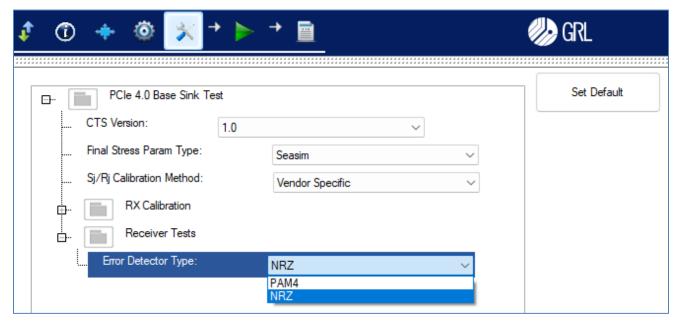

Select from the menu to access the **Configurations** page. Set the required parameters for DUT Rx testing as described below.

To return all parameters to their default values, select the 'Set Default' button.

FIGURE 36. RECEIVER TEST PARAMETERS CONFIGURATION PAGE

TABLE 5. RECEIVER TEST PARAMETERS DESCRIPTION

| Parameter           | Description                                                                                                                                        |  |  |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Error Detector Type | Select the PAM4 or NRZ error detector to be used for DUT testing. <i>Note: The MU196040B error detector module supports PAM4 BER measurements.</i> |  |  |

#### 5.2 Enable Loopback BER Test

To set up the GRL software to automate loopback testing for error detection, go to the Configurations page and set up the following settings. *Make sure that the Rx DUT is capable of supporting loopback mechanism for BER measurements.*

1. Under the Error Counter tab, select 'LoopBack' to enable loopback test mode for the DUT.

FIGURE 37. SELECT BER LOOPBACK TEST METHOD

2. Under the Loopback Mode tab, select 'Clock Recovery' in the Clock Recovery Method field to apply the clock data recovery function to process the modified compliance pattern generated by the DUT. Then, set the value for the Clock Recovery Loop Bandwidth.

If using a user-defined pattern instead of the default test pattern for error checking, select the 'Custom Pattern for Error Detector' checkbox. Then, select the type of custom test pattern to be used.

FIGURE 38. SET UP LOOPBACK TEST

3. If needed to change the default spec-defined limits for the target BER and maximum error allowed for BER measurements, then select the Compliance tab and enter new values.

FIGURE 39. SET BER/ERROR LIMITS

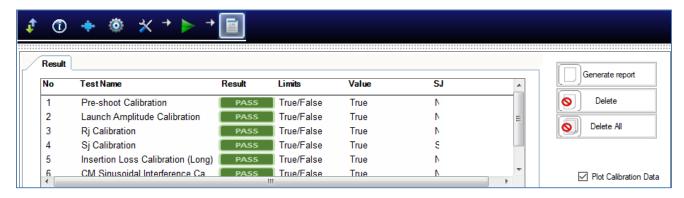

## 6 Interpreting Test Report

The **Report** page has all the results from all the test runs displayed. If some of the results are not desired, they can be individually deleted by using the **Delete** button. Also for a PDF report, select the **Generate report** button. To have the calibration data plotted in the report, make sure the **Plot Calibration Data** box is checked.

FIGURE 40. REPORT RESULTS PAGE

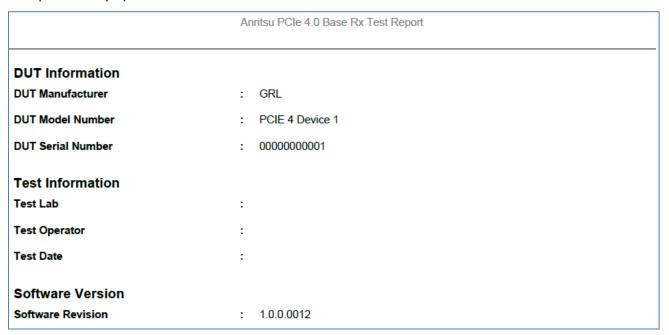

#### 6.1 DUT Information

This portion is populated from the information in the DUT tab from the **Session Info** tab.

FIGURE 41. DUT INFORMATION

#### **6.2** Summary Table

This portion is populated from the tests performed and its results. This gives an overall view of all the results and its test conditions.

| No | TestName                                 | Limits     | Value | Results | SJ     |

|----|------------------------------------------|------------|-------|---------|--------|

| 1  | PG Delay Calibration                     | True/False | True  | Pass    |        |

| 2  | Pre-shoot Calibration                    | True/False | True  | Pass    |        |

| 3  | De-emphasis Calibration                  | True/False | True  | Pass    |        |

| 4  | Launch Amplitude Calibration             | True/False | True  | Pass    |        |

| 5  | Rj Calibration                           | True/False | True  | Pass    |        |

| 6  | Sj Calibration                           | True/False | True  | Pass    | SJLF_2 |

| 7  | Sj Calibration                           | True/False | True  | Pass    | SJLF_3 |

| 8  | Sj Calibration                           | True/False | True  | Pass    | SJLF_4 |

| 9  | Sj Calibration                           | True/False | True  | Pass    | SJLF_1 |

| 10 | SJ Tone Calibration                      | True/False | True  | Pass    |        |

| 11 | DM Phase Calibration                     | True/False | True  | Pass    |        |

| 12 | CM Phase Calibration                     | True/False | True  | Pass    |        |

| 13 | Insertion Loss Calibration (Long)        | True/False | True  | Pass    |        |

|    | (Downstream)                             |            |       |         |        |

| 14 | CM Sinusoidal Interference Calibration   | True/False | True  | Pass    |        |

|    | (Long) (Downstream)                      |            |       |         |        |

| 15 | DM Sinusoidal Interference Calibration   | True/False | True  | Pass    |        |

|    | (Long) (Downstream)                      |            |       |         |        |

| 16 | Stressed Jitter Voltage Calibration      | True/False | True  | Pass    |        |

|    | (Long) (Downstream)                      |            |       |         |        |

| 17 | Insertion Loss Calibration (Long)        | True/False | True  | Pass    |        |

|    | (Upstream)                               |            |       |         |        |

| 18 | CM Sinusoidal Interference Calibration   | True/False | True  | Pass    |        |

|    | (Long) (Upstream)                        |            |       |         |        |

| 19 | DM Sinusoidal Interference Calibration   | True/False | True  | Pass    |        |

|    | (Long) (Upstream)                        |            |       |         |        |

| 20 | Stress Jitter Voltage Calibration (Long) | True/False | True  | Pass    |        |

|    | (Upstream)                               |            |       |         |        |

FIGURE 42. SUMMARY TABLE

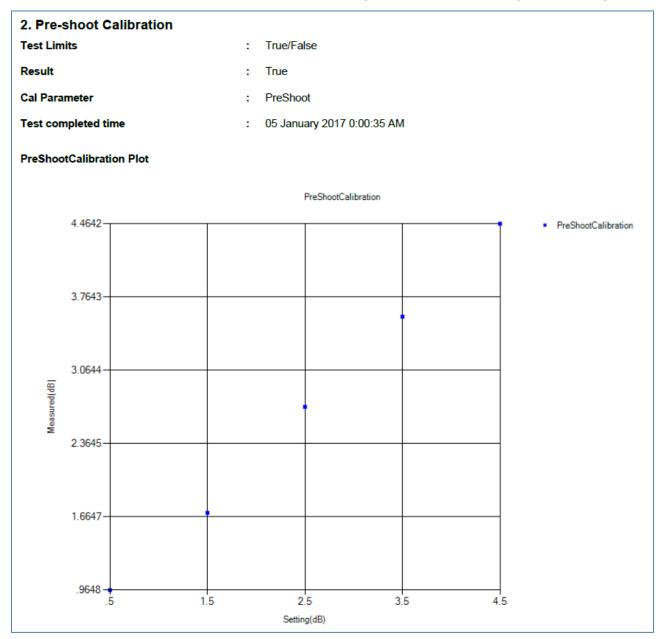

#### 6.3 Calibration Data Results

If Plot Calibration Data checkbox is checked, then the plots are shown in this part of the report.

FIGURE 43. CALIBRATION RESULTS EXAMPLE

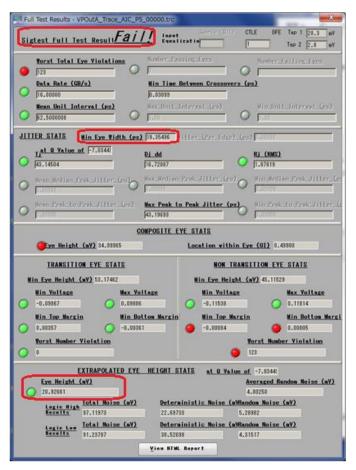

#### **6.4 Compliance Test Results**

27. Stress Jitter Voltage Test (Long) (Upstream) [SJLF\_4]

Pass/Fail Stats : Pass

Test Limits : True/False

Result : True

Test Frequency : 100 MHz

ISI Generator : Artek

Preshoot (dB) : 0 (0)

**DeEmphasis (dB)** : -6 (-6.35)

**RJ (ps RMS)** : 1 (0.24)

**SJ (ps)** : 12.5 (0.17)

Amplitude (mV) : 500 (330)

DMSI Freq (GHz) : 2.1

DMSI (mV) : 11.06383039056 (26.2475834324656)

CM Freq (MHz) : 120

CMSI (mV) : 150 (169228.754408806)

SJ Tone Freq (MHz) : 210

**SJ Tone (ps)** : 12.5 (0.17229946287562)

Max Error Allowed : 0

Error Counts : 0

Test completed time : 20 February 2018 22:47:36 PM

FIGURE 44. COMPLIANCE TEST RESULTS EXAMPLE

#### 6.5 Margin Test Results

29. Stress Jitter Voltage Margin Test (Long) (Downstream) [SJLF\_2]

Pass/Fail Stats : Fail

Test Limits : True/False

Result : False

ISI Generator : Artek

Preshoot (dB) : 0 (0)

**DeEmphasis (dB)** : -6 (-6.35)

**RJ (ps RMS)** : 1 (0.24)

Amplitude (mV) : 350 (230)

DMSI Freq (GHz) : 2.1

**DMSI (mV)** : 16.3780929451514 (42.6636011745818)

CM Freq (MHz) : 120

CMSI (mV) : 150 (168440.228264395)

SJ Tone Freq (MHz) : 210

**SJ Tone (ps)** : 12.5 (0.17229946287562)

Sj Specs : 125 UI

Max Error Allowed : 0

Test completed time : 20 February 2018 22:06:29 PM

FIGURE 45. MARGIN TEST RESULTS EXAMPLE

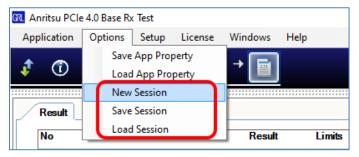

## 7 Saving and Loading Test Sessions

The GRL-PCIE4-BASE-RXA software enables Calibration and Test Results to be created and maintained as a 'Live Session' in the application. This allows you to quit the application and return later to continue where you left off.

Save and Load Sessions are used to Save a Test Session that you may want to recall later. You can 'switch' between different sessions by Saving and Loading them when needed.

To save a session, with all of the parameter information, the test results, and any waveforms, use the "Options" command on the menu bar, then the "Save Session" command.

To load a session back into the software, including the saved parameter settings, use the "Options" command on the menu bar, then the "Load Session" command.

To create a New session and return the application back to a default configuration, use "Options" command on the menu bar, then the "New Session" command.

FIGURE 46. SAVING AND LOADING CALIBRATION AND TEST SESSIONS

The configuration and session results are saved in a file with the extension '.ses', which is a compressed zip-style file, containing a variety of information.

# 8 Appendix A: Method of Implementation (MOI) Using Automation

This section provides sample methodology to automate PCIe Gen 4 Base Rx calibration using GRL-PCIE4-BASE-RXA software at 16 GT/s. This procedure will ensure Receiver Impairment adjustments on the MP1800A/MP1900A BERT are accurate before running DUT compliance tests.

#### 8.1 Perform Calibration at TP1

#### 8.1.1 Pre-shoot Calibration

The **Caltable** method is used to calibrate pre-shoot:

- 1. Set 800mV (p-p) amplitude on BERT.

- 2. Set 0dB for De-emphasis on MP1825B/MP1900A.

- 3. Measure:

```

1dB at MP1825B/MP1900A, then measure Pre-shoot, record 2dB at MP1825B/MP1900A, measure again, record 3dB at MP1825B/MP1900A, measure again, record .....

5dB at MP1825B/MP1900A, measure again, record.

```

- 4. Plot a Caltable graph.

- 5. Passing criteria is to obtain measured Pre-shoot at 1dB Min and Max 4dB.

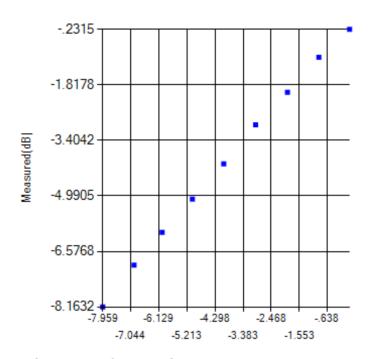

#### 8.1.2 De-emphasis Calibration

The Caltable method is used to calibrate De-emphasis:

- 1. Set 800mV (p-p) amplitude on BERT.

- 2. Set 0dB for Pre-shoot on MP1825B/MP1900A.

- 3. Measure:

- -8dB at MP1825B/MP1900A, then measure De-emphasis, record

- -7dB at MP1825B/MP1900A, measure again

- -6dB at MP1825B/MP1900A, measure again

..... 0dB.

- 4. Plot a Caltable graph.

- 5. Passing criteria is to obtain measured De-emphasis at -1dB Min and Max -6dB.

FIGURE 47. DE-EMPHASIS CALIBRATION CALTABLE GRAPH

#### 8.1.3 Launch Amplitude Calibration

The Caltable method is used to calibrate Launch Amplitude:

- 1. Initialize BERT.

- 2. Set MP1825B/MP1900A to 0dB Pre-shoot and De-emphasis obtained from Caltable as measured above.

- 3. Set 300mV Amplitude at BERT, then measure the amplitude in scope, record it.

- 4. Increase 100mV on each iteration, measure the amplitude in scope, until measured amplitude meets or exceeds 1200mV.

- 5. Plot a Caltable graph.

- 6. Passing criteria is to obtain MEAN value of Launch Amplitude measurement at 720-800mV.

#### 8.1.4 RJ Calibration

The Caltable method is used to calibrate RJ:

- 1. Initialize BERT.

- 2. Set 800mV (p-p) amplitude (based on calibrated value).

- 3. Set MP1825B/MP1900A to 0dB Pre-shoot and De-emphasis obtained from Caltable as measured above.

- 4. Set All Stress to 0mV.

- 5. Set 1100 Pattern on BERT.

- 6. Set Initial RJ value to 0.04UI(p-p) on BERT.

- 7. Measure RJ (in ps (RMS)) from scope using EZJIT, record the measured value.

- 8. Increase 0.1UI (p-p) on each iteration, measure RJ from scope, until measured RJ meets or exceeds 1.0ps (RMS).

- 9. Plot a Caltable graph.

- 10. Passing criteria is to obtain measured RJ at 1.0 ps (RMS).

#### 8.1.5 SJ Calibration

The Caltable method is used to calibrate SJ:

- 1. Initialize BERT.

- 2. Set 800mV (p-p) amplitude (based on calibrated value).