## **Granite River Labs**

# PCI Express® Gen 3.0 Base PCIe3-BASE & PCIe4-BASE (8 GT/s) Receiver Compliance Test Automation Solution User Guide & MOI

Using Anritsu MP1900A BERT, Tektronix DPO/MSO70000 Series Oscilloscope, and GRL-PCIE4-BASE-RXA Automation Test Software

Published on 15 April 2021

All product names are trademarks, registered trademarks, or service marks of their respective owners.

The GRL disclaims all warranties and liability for the use of this document and the information contained herein and assumes no responsibility for any errors that may appear in this document, nor does the GRL make a commitment to update the information contained herein.

Contact the GRL office to obtain the latest revision of this document.

Questions regarding this document in the GRL may be forwarded to:

Granite River Labs 3500 Thomas Road, Suite A, Santa Clara, CA 95054

Phone: 408-627-7608 Fax: 408-912-1810 E-mail: info@graniteriverlabs.com http://www.graniteriverlabs.com

#### **DISCLAIMER**

This document is provided "as is" with no warranties whatsoever, including any warranty of merchantability, no infringement, fitness for any particular purpose, or any warranty otherwise arising out of any proposal, specification, or sample. The GRL disclaims all liability for infringement of proprietary rights, relating to use of information in this specification. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted herein.

All product names are trademarks, registered trademarks, or service marks of their respective owners.

Copyright © 2021 Granite River Labs

## **TABLE OF CONTENTS**

| 1 | IN                              | TRODUCTION                                                                 | 9              |

|---|---------------------------------|----------------------------------------------------------------------------|----------------|

|   | 1.1                             | REFERENCE DOCUMENTS                                                        | 9              |

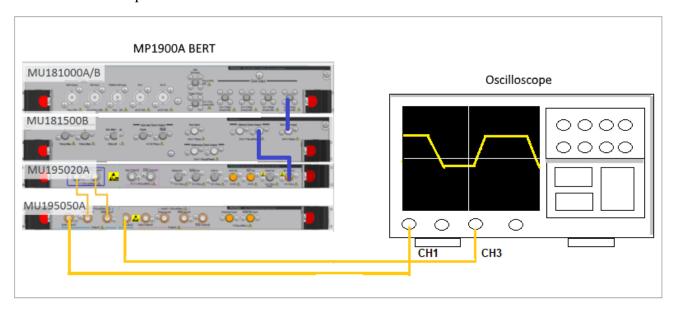

| 2 | RE                              | SOURCE REQUIREMENTS                                                        | 10             |

|   | 2.1                             | EQUIPMENT REQUIREMENTS                                                     | 10             |

|   | 2.2                             | SOFTWARE REQUIREMENTS                                                      | 11             |

| 3 | GE                              | ENERAL OVERVIEW OF PCIE BASE RX CTS REQUIREMENTS                           | 12             |

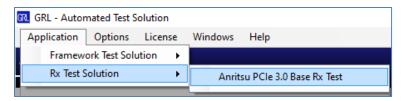

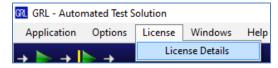

| 4 | SE                              | TTING UP GRL-PCIE4-BASE-RXA AUTOMATION SOFTWARE                            | 17             |

|   | 4.1                             | Download GRL-PCIE4-BASE-RXA Software                                       | 17             |

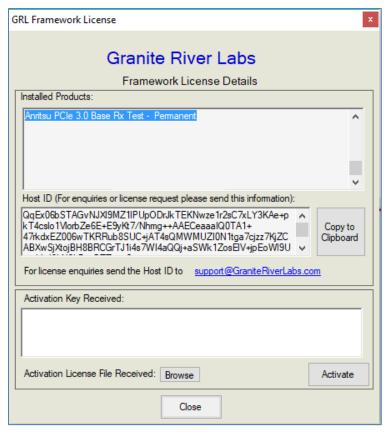

|   | 4.2                             | Launch and Set Up Software                                                 | 17             |

|   | 4.3<br>4.3<br>4.3               |                                                                            | 20             |

| 5 | CA                              | LIBRATING USING GRL-PCIE4-BASE-RXA                                         | 21             |

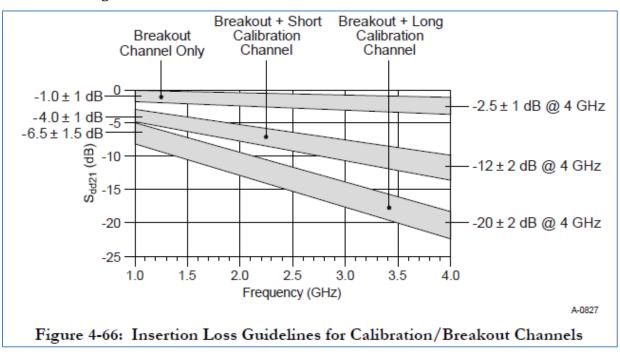

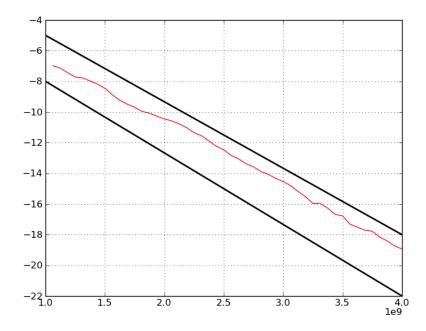

|   | 5.1                             | TP2 CHANNEL CALIBRATION INSERTION LOSS                                     | 22             |

|   | 5.2<br>5.2<br>5.2               |                                                                            | 22             |

|   | 5.3                             | SET UP AUTOMATED RX CALIBRATION FOR TP1                                    | 26             |

|   | 5.4                             | SET UP AUTOMATED RX CALIBRATION FOR TP2                                    | 27             |

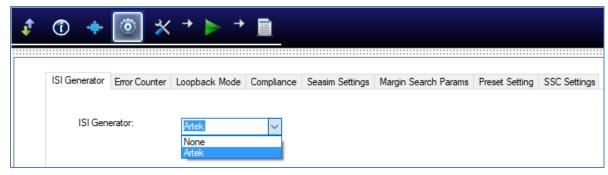

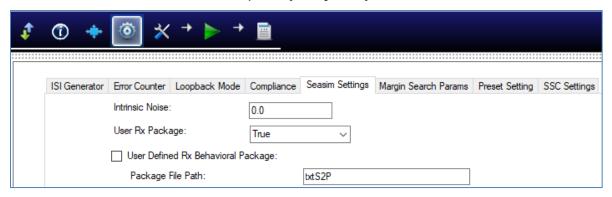

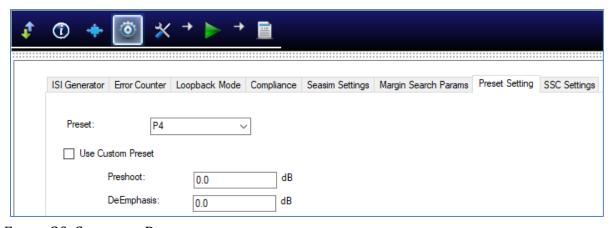

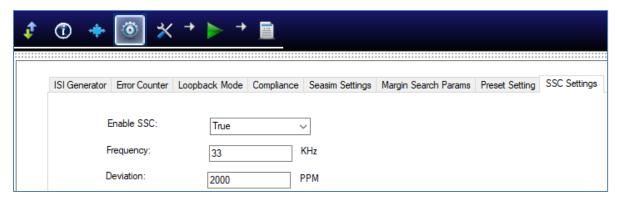

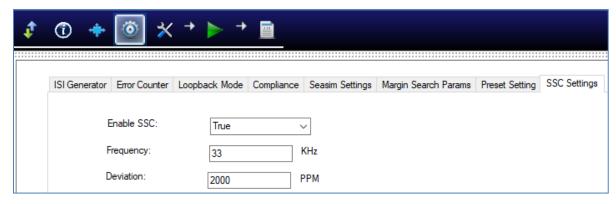

|   | 5.5<br>5.5<br>5.5<br>5.5<br>5.5 | .2 Seasim Settings Tab                                                     | 27<br>28<br>28 |

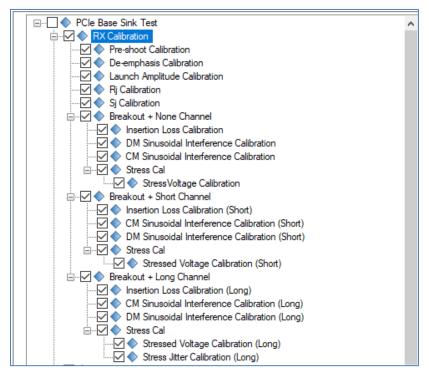

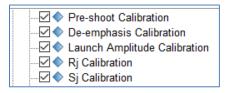

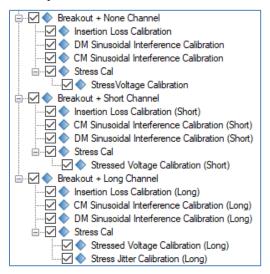

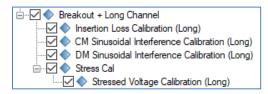

|   | 5.6                             | SELECT PCIE GEN 3 BASE RX CALIBRATION                                      | 29             |

|   | 5.6<br>5.6                      |                                                                            |                |

|   | 5.7                             | Configure Rx Calibration Parameters                                        |                |

|   |                                 | Run Automation Calibration                                                 |                |

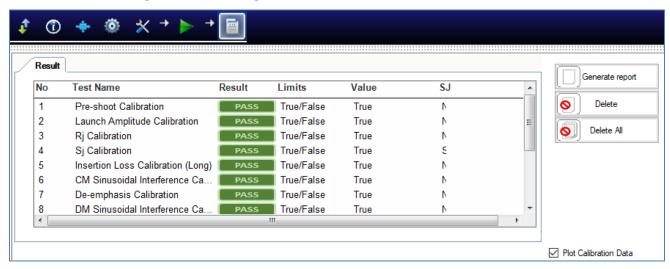

| _ | 5.8                             |                                                                            |                |

| 6 |                                 | STING USING GRL-PCIE4-BASE-RXA                                             | 33             |

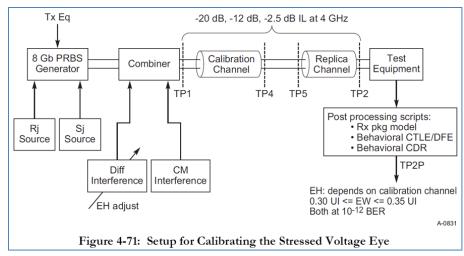

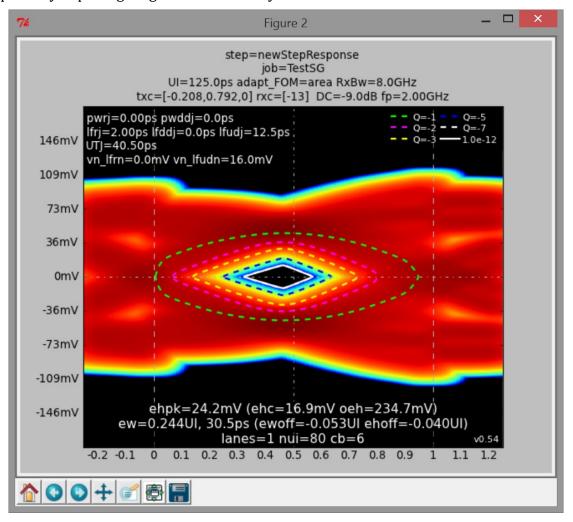

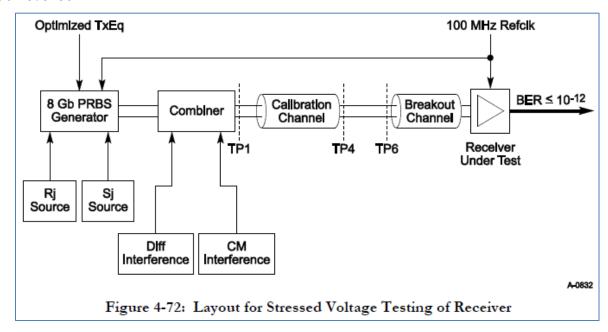

|   | 6.1                             | STRESSED VOLTAGE RECEIVER TEST                                             |                |

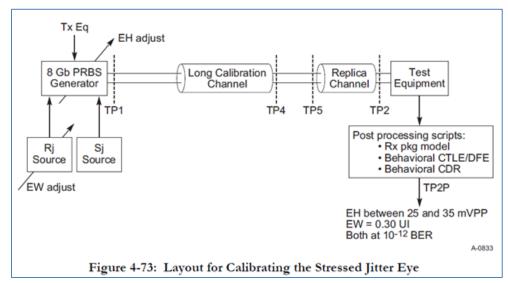

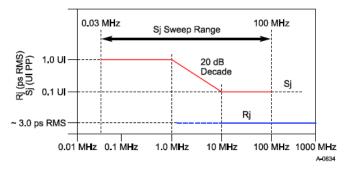

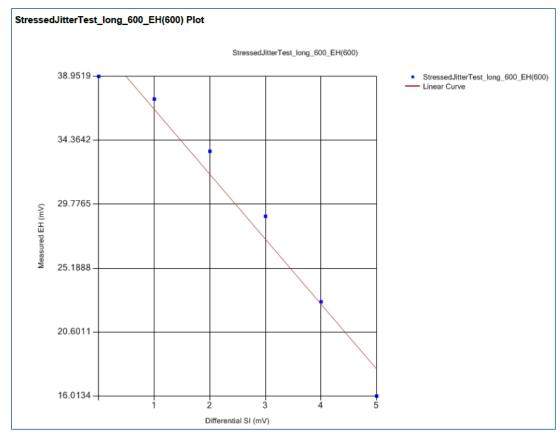

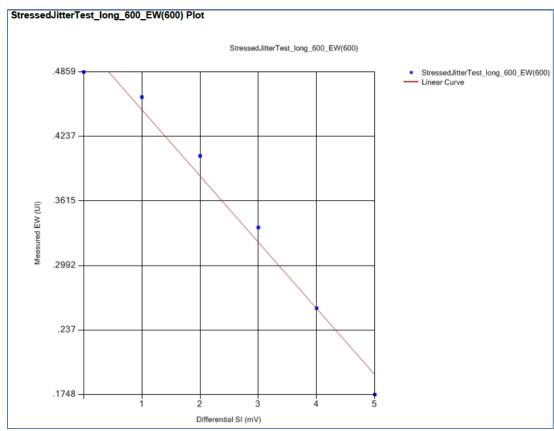

|   | 6.2                             | STRESSED JITTER RECEIVER TEST (FOR LONG CHANNEL ONLY @PCIE3-BASE RX SPECS) |                |

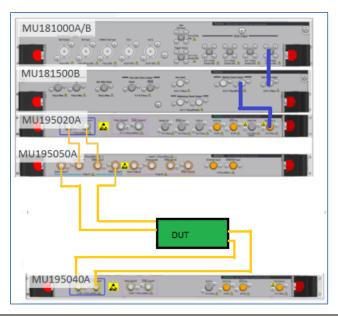

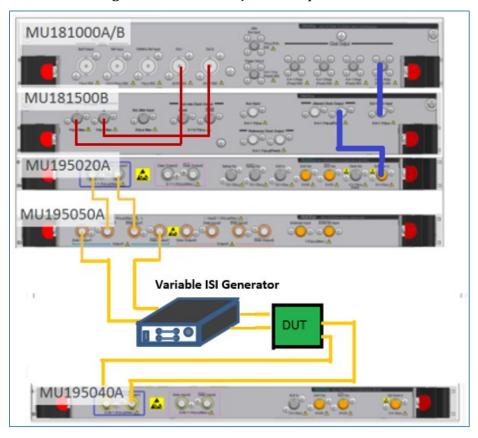

|   | 6.3<br>6.3<br>6.3               | 1 1                                                                        | 34             |

| 6.4 Set Up Test Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 36                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

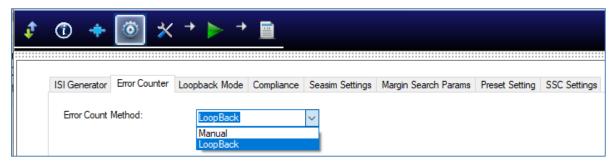

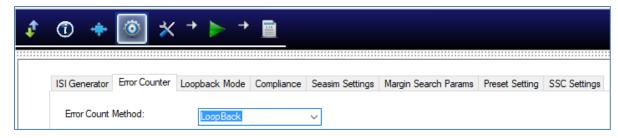

| 6.4.1 Error Counter Tab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 36                               |

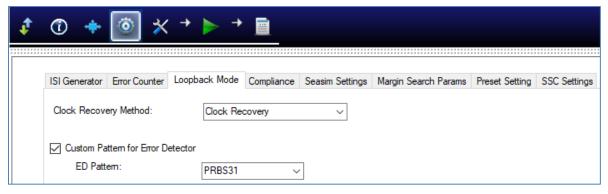

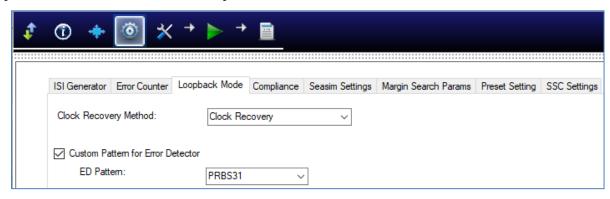

| 6.4.2 Loopback Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                  |

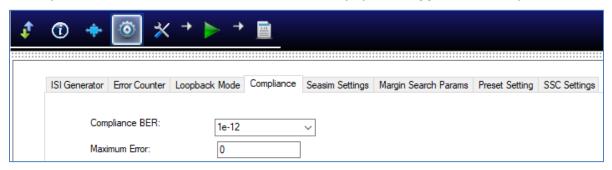

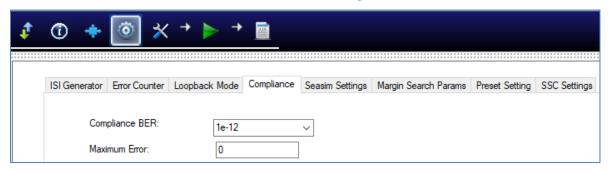

| 6.4.3 Compliance Tab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                  |

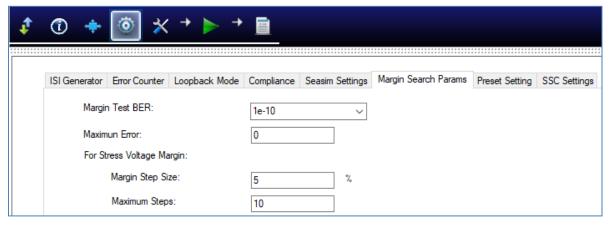

| 6.4.4 Margin Search Parameters Tab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                  |

| 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                  |

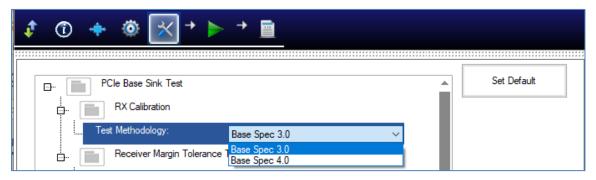

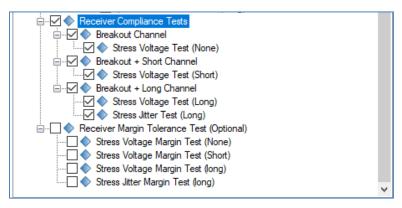

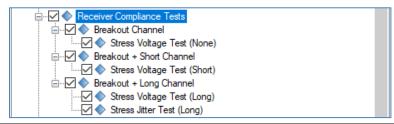

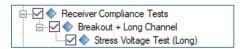

| 6.5 SELECT PCIE GEN 3 BASE RX DUT TESTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                  |

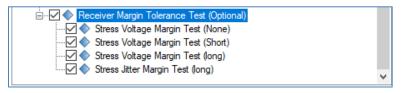

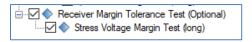

| 6.5.2 Select to Run Rx Margin Tolerance Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                  |

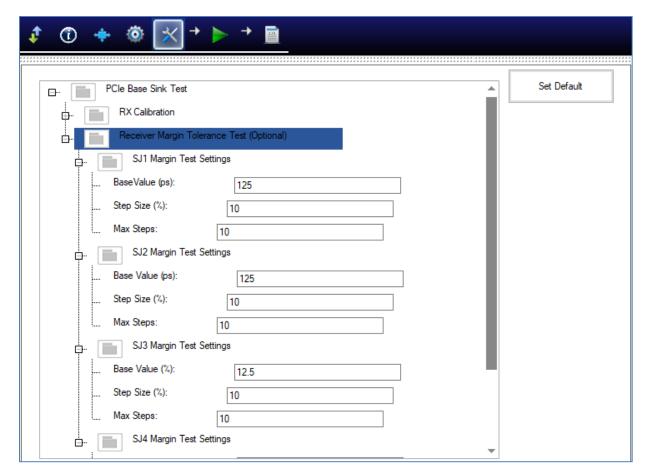

| 6.6 CONFIGURE MARGIN TOLERANCE TEST PARAMETERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                  |

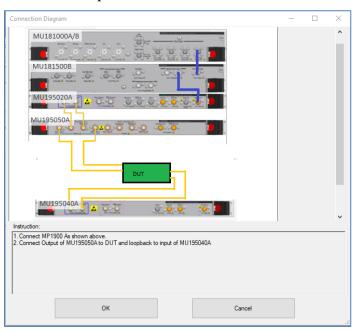

| 6.7 Enable Loopback BER Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                  |

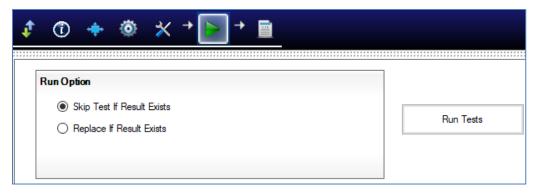

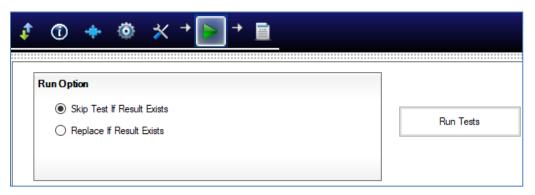

| 6.8 Run Automation Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                  |

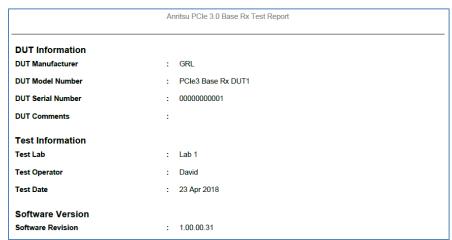

| 7 INTERPRETING GRL-PCIE4-BASE-RXA TEST REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 43                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                  |

| 7.1 Understand Test Report Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                  |

| 7.1.1 Test Session Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                  |

| 7.1.2 Test Summary Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                  |

| 7.2 Delete Test Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                  |

| 7.2 DELETE TEST RESULTS  8 SAVING AND LOADING GRL-PCIE4-BASE-RXA TEST SESSIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 47                               |

| SAVING AND LOADING GRL-PCIE4-BASE-RXA TEST SESSIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 47                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 47                               |

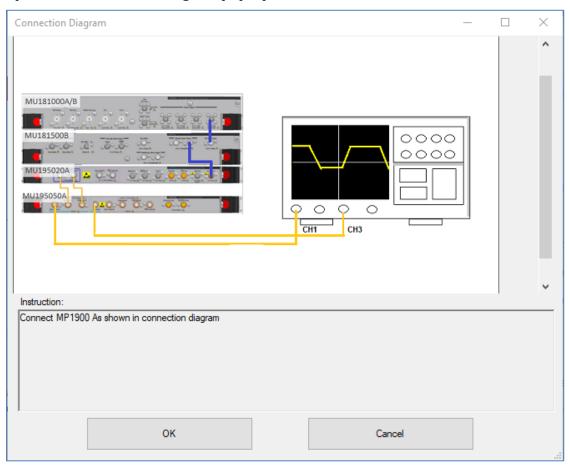

| SAVING AND LOADING GRL-PCIE4-BASE-RXA TEST SESSIONS APPENDIX A: METHOD OF IMPLEMENTATION (MOI) USING AV 48 9.1 Perform Calibration at TP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>47</b><br>UTOMATION<br>48     |

| SAVING AND LOADING GRL-PCIE4-BASE-RXA TEST SESSIONS  APPENDIX A: METHOD OF IMPLEMENTATION (MOI) USING AVAIDABLE AND AVAIDABLE AN | <b>47 UTOMATION</b> 4848         |

| SAVING AND LOADING GRL-PCIE4-BASE-RXA TEST SESSIONS  APPENDIX A: METHOD OF IMPLEMENTATION (MOI) USING AVAIDABLE AVAI | <b>47 UTOMATION</b> 484848       |

| SAVING AND LOADING GRL-PCIE4-BASE-RXA TEST SESSIONS  APPENDIX A: METHOD OF IMPLEMENTATION (MOI) USING AVA  48  9.1 Perform Calibration at TP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>47 UTOMATION</b> 48484849     |

| SAVING AND LOADING GRL-PCIE4-BASE-RXA TEST SESSIONS  APPENDIX A: METHOD OF IMPLEMENTATION (MOI) USING AVA  9.1 Perform Calibration at TP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>47 UTOMATION</b> 48484849     |

| SAVING AND LOADING GRL-PCIE4-BASE-RXA TEST SESSIONS  APPENDIX A: METHOD OF IMPLEMENTATION (MOI) USING AVA  9.1 PERFORM CALIBRATION AT TP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>47 UTOMATION</b> 4848494950   |

| SAVING AND LOADING GRL-PCIE4-BASE-RXA TEST SESSIONS  APPENDIX A: METHOD OF IMPLEMENTATION (MOI) USING AVA  9.1 PERFORM CALIBRATION AT TP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>47 UTOMATION</b> 4848494950   |

| SAVING AND LOADING GRL-PCIE4-BASE-RXA TEST SESSIONS  APPENDIX A: METHOD OF IMPLEMENTATION (MOI) USING AVA  9.1 PERFORM CALIBRATION AT TP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 47 UTOMATION4848495051           |

| SAVING AND LOADING GRL-PCIE4-BASE-RXA TEST SESSIONS  APPENDIX A: METHOD OF IMPLEMENTATION (MOI) USING AVA  9.1 PERFORM CALIBRATION AT TP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 47 UTOMATION484849505151         |

| SAVING AND LOADING GRL-PCIE4-BASE-RXA TEST SESSIONS  APPENDIX A: METHOD OF IMPLEMENTATION (MOI) USING AVA  9.1 PERFORM CALIBRATION AT TP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 47 UTOMATION4848495051515455     |

| SAVING AND LOADING GRL-PCIE4-BASE-RXA TEST SESSIONS  APPENDIX A: METHOD OF IMPLEMENTATION (MOI) USING AVA  9.1 PERFORM CALIBRATION AT TP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 47 UTOMATION4848495051515455     |

| SAVING AND LOADING GRL-PCIE4-BASE-RXA TEST SESSIONS  APPENDIX A: METHOD OF IMPLEMENTATION (MOI) USING AVA  9.1 PERFORM CALIBRATION AT TP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 47 UTOMATION4848495051515455     |

| SAVING AND LOADING GRL-PCIE4-BASE-RXA TEST SESSIONS  APPENDIX A: METHOD OF IMPLEMENTATION (MOI) USING AVA8  9.1 PERFORM CALIBRATION AT TP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 47 UTOMATION484849505151555555   |

| SAVING AND LOADING GRL-PCIE4-BASE-RXA TEST SESSIONS  APPENDIX A: METHOD OF IMPLEMENTATION (MOI) USING AVA8  9.1 PERFORM CALIBRATION AT TP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 47 UTOMATION48484950515154555555 |

| SAVING AND LOADING GRL-PCIE4-BASE-RXA TEST SESSIONS  APPENDIX A: METHOD OF IMPLEMENTATION (MOI) USING AVA  9.1 PERFORM CALIBRATION AT TP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 47 UTOMATION48484950515555555555 |

| <b>12</b> | APPENDIX D: CONNECTING TEKTRONIX OSCILLOSCOPE TO PC | 63        |

|-----------|-----------------------------------------------------|-----------|

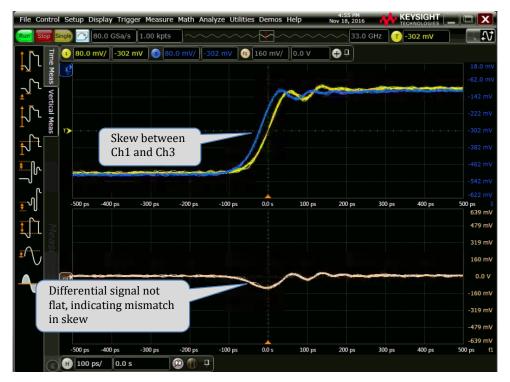

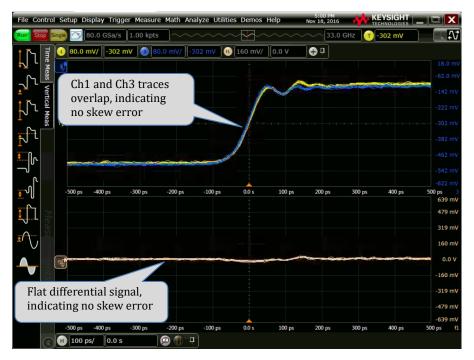

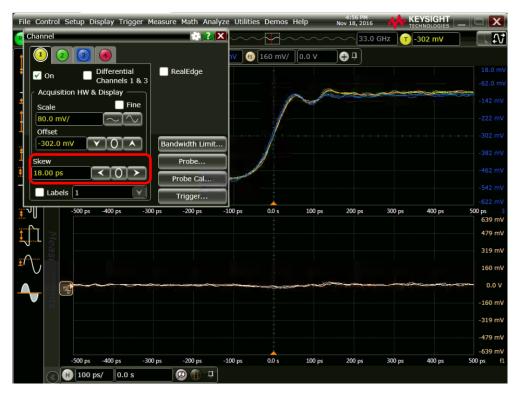

| 13        | APPENDIX E: SCOPE AND CABLE DE-SKEW                 | <b>65</b> |

|           |                                                     |           |

|           |                                                     |           |

|           |                                                     |           |

|           |                                                     |           |

|           |                                                     |           |

|           |                                                     |           |

|           |                                                     |           |

|           |                                                     |           |

|           |                                                     |           |

|           |                                                     |           |